【デジタル・モード・トランシーバ:ADX-S製作】

abstract

The ADX-S is a modification by BD2CR Adam Rong of the ADX digital mode shortwave transceiver developed by WB2CBA Barbaros Asuroglu. Both software and hardware are open source and information is available on GitHub. He referred to my Blog article when he improved the ADX-S. I was wondering what part of my Blog he referred to. I contacted the distributor, JL1KRA Nakajima-san, and asked him to distribute it. The reference was a Blog article about a shortwave receiver using the TA2003P chip for radio. Then I received a request from Mr. Rong to improve AGC. I immediately experimented with it and the conclusion is that AGC is not necessary for ADX-S. (2024.04.24 de JA9TTT/1 Takahiro Kato)

【ADX-Sキットが届く・・・】

ADX-Sと言うシンプルなトランシーバのキットが好評なようです。JA局へ頒布を仲介されているJL1KRA:中島さんのサイトを拝見していると頒布の開始、すぐ品切れの状況です。

このADX-Sですが聞く所によるとJA9TTTのBlog情報を参考にしているとのこと。どんな所を参考にしているのか興味を覚えたのです。まあ、興味というよりちょっと心配になったと言った方が良いかも知れません。 Blogを参照した「いかなる結果にも責任は負わない」って書いてはいますが気になりました。(笑)

もう昨年のことですが、お問い合わせ致したところJL1KRA:中島さん、開発者のBD2CR:Adam Rongさんのお世話で製作する機会が持てました。どうもありがとうございました。

☆

勿体ぶってもしょうがないので、さっさと書いてしまいましょう。それは何かと言うと:このBlogにはTA2003Pと言うラジオ用のICチップを使い短波ラジオを作ると言う話(←リンク)があります。それを参考にしたそうです。その短波ラジオにはCWやSSBを聞く目的でBFOが付いています。この辺りが一般の短波ラジオとは違うところですが、それをADX-Sの受信部に採用したようです。

ADX-Sにはその元になるトランシーバが存在します。WB2CBA / Barbaros Asuroglu氏が設計したADXと言うものです。周波数と送受信の制御にAruduinoマイコンを使うものでプログラムほかオープンソースになっています。興味を覚えたようなら検索すればGitHubに情報が見つかります。

ADXも受信部にTA2003Pを使うことは同じですがTA2003Pのミキサ部を検波に使ったダイレクト・コンバージョン形式です。ではADX-Sは何が違うのかといえばADXが検波に使っていたミキサ部を本来の用途であるコンバータ回路として使ったところです。要するにDC受信機からスーパ受信機に発展させたのです。スーパ・ヘテロダインの「S」を付けて型番をADX-Sとしたのでしょう。この改良はBD2CR / Adam Rong氏によって行なわれました。ADX-Sも同じくオープンソースになっています。

ADXがADX-Sになって向上したのは「感度」に違いありません。I-F Ampのゲインが加わるのですから30〜40dBはゲインがアップします。オリジナルのADXの使用経験はありませんが、やはり感度では差が付くのではないでしょうか。 あまり良いアンテナが望めない移動運用に於いてはアップした感度はたいへん有益なはずです。

【メイン基板の製作】

製作方法の詳細を書くのはこのBlogの役目ではありません。作り方や手順はJL1KRA:中島さんの頒布サイト(←リンク)に詳しく解説されています。Kitに付属のドキュメントも良く参照する必要があります。

Kitは始めに部品の過不足がないか確認する作業がとても大切です。確認しながら分類しておくと製作がスムースに進みます。付いてきた部品の形状を把握しておけば実装する際の注意ポイントもわかってきます。 もちろん製作の工程と手順の確認も重要なポイントです。 プリント基板の表裏を間違えると言ったポカミスも防げるはずです。

以前、古くからキット頒布されているお方に伺ったことがあるのですが、こうした基本の作業を怠っていきなりハンダ付けを始める人がいるそうです。

傾向として、ちゃんとやらないのは意外に「OMさん」に多いんだそうです。それでつまらん失敗の挙句、頒布者にクレームが来るんだとか。しかも言うことだけはご立派なくせに、返却品を見たらいい加減なことは一目瞭然だそうで・・・ハンダ付けさえも怪しいとか。大のオトナがみっともないくらいだそうです。(笑)説明書読むのは煩わしいかも知れませんが先ずは読んでみて手順の通りにやった方が確実ですね。恥もかかずに済みます。w

少ないとは言っても写真のような部品があります。 普通の電子回路にはそれほど冗長性はありませんから、ハンダ付けが1ヶ所マズイだけでもきちんと働きません。 適切なハンダコテを使い確実なハンダ付けを心がける必要があります。

両面パターンのスルーホール基板です。一旦ハンダ付けしてしまうと専用のリペアツールが無ければ付け直しは「かなり困難」です。特に足の多い部品は間違えないように挿入します。 ハンダコテは弱い物(ワット数が小さい物)よりもややパワーのある物を使った方が確実です。 弱いコテを長い時間当てるよりもパワーのあるコテで短時間でサッと済ませる方が部品へのダメージも少ないものです。

付属部品の分類・整理を済ませてから、通電・動作テストできる状態までに必要な製作時間は5時間くらいでしょう。これにはLPFモジュール(下記)を1つ作る分も含まれます。私の場合、写真撮影や簡単な測定評価の時間も含んで昼から始めて夕方にはテストできる状態になりました。製作をじっくり楽しみながら実質5時間くらいで作れそうな規模のKitです。

【LPFモジュール製作】

オンジエアする際はLPFモジュールをバンド毎に付け替える必要があります。このLPFモジュール部分の製作が意外に面倒でした。

各モジュール毎に3個ずつコイルを巻く必要があるからです。(全部で4バンド分ですから12個も!) 2つがLPF(ローパスフィルタ)用で、一つがD級アンプの負荷コイルです。

コイルの部分は部品を所定の場所にハンダ付けするだけでは済まないので時間が掛かります。 手際良く進めても1つのバンドあたり30分くらい掛かるでしょう。 だんだんコイル巻きにも慣れてくるので最後の方はもうちょっと早く作れるかも知れませんが・・・。

【ADX-Sの回路】

左の回路図を見れば非常にシンプルなトランシーバとわかるでしょう。

制御回路にArduino nanoマイコンボード、周波数シンセサイザにSi5351ボードと言った既成のモジュールを使い外付け部品が最小限で済むよう工夫されています。

重要な周波数シンセサイザ部は定番のSi5351モジュールで、これ一つで送信、受信局発、BFOの3つの発振器の機能を実現しています。 組立の過程で周波数キャリブレーションを行なって十分な周波数精度が得られるようになっています。 FT-8用としてはマズマズの周波数安定度が得られていると思いました。WSPRには少し厳し感じですかね。

受信部はラジオ用ICのTA2003Pを使っています。TA2003Pはもともと外付けの少ないICですがアンテナコイルを省く、局発は外から与えると言った方法で簡略化しているのがわかるでしょう。TA2003Pの検波出力は何も増幅せずに復調用パソコンのマイク端子へ送られます。

送信部も見ての通り簡単な構造です。 Si5351の出力を高速C-MOSの74ACT244で強化して終段をドライブします。終段アンプはBS170と言う小型Power-MOS FET(3本パラ)を使ったD級アンプになっています。これで高効率に出力電力2〜4Wを得ています。

【LPFモジュールの回路】

ローパス・フィルタ部は小さな基板モジュールになっています。

運用するHAMバンドに応じてメイン基板のコネクタに挿入します。 バンドを変更するたびにLPFを交換しスイッチでバンド設定せねばならないので少し面倒臭いです。

しかしたいへんシンプルな構造のトランシーバですからやむを得ないでしょう。 慣れればそれほど面倒とも感じなくなりそうです。(笑)

【ADX-S完成】

意外に時間がかかったのはプラケースの加工でした。(上記の5時間にはケース加工は含まれません) ポリエチレンで出来た半透明の収納ケースは中途半端に柔らかくて加工しにくいのです。見ての通り出来栄えはあまり宜しくありません。w

たぶん適切な加工用工具と作業方法があるのでしょう。 しかしコツを掴む前に完成してしまいました。(笑)

ADX-Sのバンドごとの出力パワーを測ってみました。

40m Band Po=2.9W 消費電流=510mA

20m Band Po=3.4W 消費電流=550mA

15m Band Po=1.7W 消費電流=390mA

10m Band Po=1.6W 消費電流=410mA

・・・のようになりました。電源電圧は12Vです。負荷は50Ωの終端型パワー計です。

ファイナルのBS170はRFアンプ用ではなくて単なるスイッチング用MOS-FETなのでハイバンドで効率が落ちるのは仕方ないと思います。ドライブも掛かりにくくなってくるのでしょう。

受信感度はなかなか良好で十分実用的だと思います。拙宅ではメインにIC-756proを使っていますが受信状況に大きな違いは感じられませんでした。 超強力なローカル局がオンジエアすると言った環境では厳しいと思いますが、そうしたことさえ無ければ問題はないでしょう。よく聞こえ(見え)ます。

ADX-SはAndroidスマホと組み合わせて使う人が多いようです。アプリにFT8CNを使うと自動交信まで可能だそうです。 まあそこまでして面白いかどうかは別ですが・・・。 Androidスマホが手に入ったら試してみたいと思いますが寝ていて知らぬまに交信済カントリが増えるなんて何か意味ってあるんですかね?(爆)

もちろんWSJT-XやJTDXと言ったパソコン用のアプリでオンジエアすることもできます。心配いりません。アナログ・インターフェースで使います。

☆ ☆ ☆

ADX-S製作の話はここでおしまいです。 続いてこの先は改造検討をする話になります。

【AGC回路の検討】

私のBlogにあるTA2003Pを使った短波ラジオの回路ではAGCが効かせてあります。その代わり注入するBFOはなるべく絞って最低限必要な大きさに調整する必要がありました。

Blogで作る短波ラジオのコンセプトは「単なる短波ラジオ」なのでBFOの機能はおまけ程度です。ですからそれでも良かったのですが、HAM専用受信機ともなると事情も変わります。 ADX-Sが組立Kitなのも厄介で製作者個々にBFOの注入レベルを調整しろとは言えないでしょう。 そこでADX-SではBFOをFT-8などの信号復調に十分なだけ(強く)注入しています。

もし、そのままAGCを働かせたなら注入したBFO信号でAGCが掛かってしまいI-F Ampのゲインが抑制されてしまいます。これでは感度が低下してマズイです。そのためADX-Sの回路ではAGCをGNDにバイパスしてその機能を無くしています。常にフルゲインで動作する状態になっています。

BD2CR / Adam Rongさんもこの辺りに課題を感じたらしく、ADX-SにAGCは掛けられないだろうかというご提案をいただきました。 写真はAGC回路の実験の様子です。

【TA2003Pに外からAGCを掛ける】

TA2003Pはオールインワンのラジオ用ICなので回路の途中を切り離すと言った工夫は出来ません。そのためI-F Amp.の終段から信号を取出してAGC用の信号を作る・・・と言ったような手法は不可能です。

可能性があるとしたらオーディオAGCということになります。BCLラジオのようなAM受信機の場合オーディオAGCはうまくありませんが、SSB/CWそしてFT-8などデジタルモードの受信なら十分な可能性があります。

図はADX-SにAGCを付加する回路です。検波出力を十分に増幅し整流したあとOP-Ampのバッファアンプで外からAGCを掛けるというものです。 TA2003PのAGC機能を解析しIC内部の駆動インピーダンスなどを検討して、図のように外部から強引にAGCを掛けても支障ないことを確認してあります。(内部のAGCは抑制されます)

TA2003Pの回路構成上の制限から本格的な通信型受信機のようなAGC特性は望めませんが少なくとも40dB以上のAGCレンジが得られました。 ADX-Sの改良は別としてもTA2003Pでデジタルモードを含めSSBやCWの受信機を作るにはマズマズの方法でしょう。強めのBFOを注入して、しかもちゃんとAGCを効かせられます。Sメータももちろん付けられます。

Rongさんのご要望にはお応えしたつもりなのですが、オーディオAGCはあまりお気に召さなかったようです。 なのでこれ以上進めるつもりもないためラフな手書きのメモでおしまいです。ちょっと見にくいかと思いますがあしからず。(笑)

☆

通信型受信機に造詣の深いお方がADX-Sの回路を見たら驚愕(卒倒?)するでしょう。 何しろ受信機の3S(感度、選択度、安定度)の2つがないがしろです。 まあ周波数安定度は周波数シンセサイザですから良いとして・・・。

受信のイメージ・レシオはほぼ0dBです。選択度もラジオ用セラフィルですから・・・。

もちろんきちんとした受信機のセオリーから言ったら幾らでもダメ出しができるでしょう。しかし実際に使ってみたら結構な実用性を発揮するわけです。

私は「これはシンプルさを楽しむ手作り品」なのだと納得しました。QRPな送信部には十分すぎる高感度です。 たぶんADX-Sはこのままが良いです。(必ず併用することになるパソコンやスマホアプリの信号処理能力が非常に高いからでもあります)

蛇足になりますがAGCについて付け加えます。 現実の問題としてAGCの付加は必須ではないと思いました。 他局より極端に強いローカル局がオンジエアしているような時にはAGCが掛かって歪みを抑えられます。しかしこれは稀なケースです。 あまりゲインのないTA2003Pの受信部は常にフルゲインであっても歪んで困るようなことは稀なのです。

HAMの電波は「かぼそく」てAMラジオ局のようにバカに強くはありませんからね。 ですからAGCはあっても無くても受信成績にはほとんど差が出ないのです。ならばAGCなんて無くても良いしそれが合理的と言うものです。今のままで良いのではありませんか? ・・・と言うのが私なりの結論です。あなたのお考えは如何でしょうか? ではまた。 de JA9TTT/1

(おわり)fm

Radio Experimenter's Blog

Something NEW for your eyes !

2024年4月24日水曜日

2024年4月9日火曜日

【Antenna】Making a Duo-Band Whip Antenna

【14MHzと18MHzの2バンド・ホイップ・アンテナ】

abstract

I built a duo-band antenna for 14 MHz and 18 MHz. But the performance of that antenna was poor. The RF Power radiation efficiency was not good. The reason was the stainless steel antenna element. The antenna was a shortened version with a loading coil. The presence of stainless steel in the magnetic field of the coil caused a loss of RF power. I was able to improve the situation by dropping the stainless steel material and replacing it with brass material. I would not have experienced this if I had used toroidal coils instead of air-core coils. However, toroidal coils have other problems. (2024.04.09 de JA9TTT/1 Takahiro Kato)

【昔っから言いますが・・】

HF帯(短波帯)のモバイル用ホイップ・アンテナの話題が続きます。 そもそもHF帯でモバイル運用したいなんて言う物好きなHAMは稀でしょうから、そんなアンテナの話は飽きてきたのではありませんか? 前回の7MHz用でおしまいにしようと思ってました。

今回は14MHzと18MHzの2バンド用アンテナを作りますが、それを紹介するのは主だった目的ではないのです。

残念ながらはじめに作ったものは低性能なアンテナになりました。 何でも成功する訳じゃありません。むしろ「失敗作」と言って良いでしょう。 なぜなのかしばらく悩んだのですが、むかし聞いたことのある話を思い出したのです。自分の経験ではないのでうろ覚えでしたがそれを切っ掛けに解決することができました。 ・・・どうやら成功の元になったようです。

☆

私自身では面白い経験だったのですが大抵のお方にとっては何か意味があるとも思えません。 いつ何をやったらどうなったのかと言う自身の備忘が主目的です。 モバイルからHFにオンジエアの最終回の話しはあいも変わらず雑談チックになりますが悪しからず。 この先はお薦めもしませんので、もしお暇でもあったら眺めてみて下さい。 暇つぶしくらいにはなるでしょう。(ココを見てる時点であなたは暇人ですが・笑)

ー・・・ー

【トロイダル・コイルは】

最初の写真はトロイダル・コイルですがこの先の話には出てきません。トロイダル・コイルで短縮アンテナの「ローディング・コイルを」と目論んでました。High-Qという先入観からです。

結論としてトロイダル・コイルは周波数特性が悪く不適当でした。特定の周波数範囲ではかなりHigh-Qですが空芯コイルと比べ高いQが保てる周波数範囲はずっと狭いのです。

条件に合う単一バンドの短縮アンテナならある程度使える可能性はあります。しかし複数のHAMバンドにまたがるアンテナには向きません。

またHigh-Qとは言っても最適化された空芯コイルを凌駕するほどの性能は難しそうです。 磁気コアによる鉄損や磁束飽和の観点から言っても短縮アンテナには空芯コイルが無難だと言う結論です。 トロイダル・コイルは回路用部品であってこうした短縮アンテナ用ではないようです。(私見です)

【移動式容量冠】

HF帯ハイバンド・・・14MHz以上のHAMバンドへオンジエアしたいと思いました。

2024年は黒点周期:サイクル25の極大期にあたります。極大期にはHF帯のハイバンドが活性化します。 まさしくDXingのチャンスです。

チャンスを逃すのは惜しいです。11年後のサイクル26は生きてないかも知れません。 POTAなどのモバイルでもオンジエアが楽しめるようにHF帯ハイバンドの移動用アンテナを作ってみます。

☆

ところが手持ち部材が底を突いてきました。買わずに済ませるには工夫が必要でした。

今回もセンタ・ローディング形式で作りましょう。 7MHzのアンテナ製作のとき切り残ったグラスファイバ・ロッドを使います。そのため全体に細くてコイルの下部セクションとしては少々貧弱です。できたらもっと長さも欲しいところです。 しかし波長は20mあるいは17mとLow-Bandよりずっと短いので何とかなるでしょう。軽量に作れば強度も大丈夫そうです。

使うことにしたグラスファイバ・ロッドは先端が細いため前作のような方法でロッド・アンテナを繋ぐことはできません。 そこで持っていたステンレス(SUS)製のロッド(φ3mmの棒)を上部エレメントとして使いました。長さは820mmあります。もともとグラスファイバ・ロッドの先端に付けるための部材でした。アンテナ用として先端に金属球も付いてます。

しかしこれを使うと上部セクションの長さを加減できないのが大きな問題でした。コイルのタップ切換だけで共振周波数をシビアに追い込むのは難しいからです。

写真は共振周波数を微調整するのための移動式の容量冠(キャパシティ・ハット)です。 ミノムシ・クリップで挟む位置をスライドして共振点を微調整します。思っていたよりも調整可能な周波数範囲が狭いのはやや不満でしたが試行錯誤を繰り返してある程度うまく行きました。

【タップ式コイル】

2バンドアンテナはローディング・コイルのタップ切換えで実現します。 ほかにトラップ式で作る高級な方法もありますが初期調整はかなりの困難が予想されます。

運用時のバンド切替えは少々面倒くさいですがタップ選択式を採用しました。 ミノムシ・クリップによるタップ切替えには幾分不安を感じます。 ただしコイルより先の部分はRF電流が少なくなるので旨くタップを引き出せば何とかなるでしょう。

こんどはバンドチェンジのたびにコイル容器を開閉します。この保護容器は開閉が容易なのは好都合でした。

【14MHz and 18MHz Whip Antenna】

下部セクションが細くて華奢な感じがします。しかし走行しながらの運用はしないので折れることはないでしょう。

全体的に軽量にできたのでアンテア基台の負担が少ないのはFBです。 流石に3つ目ともなれば目新しさはぜんぜん感じませんがマズマズの出来映えです。(・・・と自画自賛・笑)

家人には「同じのを3つも作ってどうするの?」なんて言われてしまいました。 確かに同じにしか見えないかな。(笑)

【残念ですが解体します】

何が問題かといえば送信時のロスが大きいことです。ローディング・コイルのあたりで発熱がありどうも輻射効率が低いようなのです。

見ての通り過去2作とほとんど違わず何が原因なのか悩みました。 結論から述べてしまうとステンレス・ロッドがコイル内に掛かっていることが損失発生の原因でした。 原因がわかれば対策しなくてはなりません・・・。

思い出したのはずいぶん前の話です。さるHAM局がモバイル用アンテナを作ったそうですが飛びが悪いと言うのです。細かい症状は忘れましたがコイル部分にかなりの発熱があるとのこと。そして輻射エレメントにステンレス材を使ったセンター・ローディング形式らしかったのです。

その時は構造など詳しくお聞きした覚えがあります。ただ、私には何が原因なのかすぐには思い浮かびませんでした。 あとでそのアンテナを良く見せてもらう機会があったのですが器用なお方らしく丁寧にそして見栄えも良く美しく仕上げてあったことを思い出します。

その後どうなったか記憶にないので、そのHAM局は諦めてしまったのかもしれません。 そして今回は私がよく似た現象に遭遇した訳です。 以下は問題検証の様子です。

【ローディング・コイルのQ】

アンテナ製作に使っているコイルは実績のあるものです。

念のために改めて確認していますが、写真のようにQu=265くらいあります。(巻数が少なく周波数が高いのでややQが低下)

巻き数や測定周波数によって変化しますが、だいたい300前後が得られます。エアダックス・コイルとして正常でしょう。

【ロッド・アンテナをコイルに挿入】

従来の構造である、ロッド・アンテナがコイルの端部に掛かった(挿入された)状態を再現してみます。

少しインダクタンスの変化とQの減少が認められます。ただしQu=225くらいあるのでそれほど大きな減少ではありませんでした。もっと低下するかと思っていたので意外でした。

そういえば、コイルのインダクタンス調整に真鍮コアを使うと言う話を思い出しました。FMやTVのチューナと言ったVHF帯のコイルのインダクタンス調整に使っているとのこと。 Qの低下を来さずにインダクタンスを加減する(減らす)ことができるので使っているのでしょう。

使っている伸縮式ロッド・アンテナ(6段式)は真鍮にクロームメッキしたパイプが使われています。 そのためQの低下をあまり来さずに済んでいるのでしょう。

【ステンレス・ロッドでQ低下】

今度は実際にアンテナに使ったステンレス・ロッドをコイル端部に挿入してみました。

幾らかインダクタンスも変化しますが、それ以上にQuの低下が顕著です。 約半分のQu=130になってしまうのです。

265だったQuが半分以下になったら損失は倍増です。 そうでなくてもローディング・コイルにはロスがあるのに損失が2倍になったら電波の飛びが悪くなって当然ですね。

アンテナの部材としてステンレス材は悪くはないと思っています。しかし使い方を考えないと性能低下をきたすことがあるのです。良い勉強になりました。

☆

ステンレス製の上部セクションを真鍮製のロッド・アンテナに交換することで対策しました。 実績のある方法へ戻ったわけです。 使っているグラスファイバ・ロッドの先端部は細いので、その先に付けるロッド・アンテナとの結合方法を考える必要がありました。これにはアクリル樹脂製のパイプに両方を挿入する形式で接続しています。

アンテナの上部セクションが伸縮可能になったので移動式の容量冠(キャパシティ・ハット)はやめました。 また波長で考えて上部セクションの長さは十分に得られているので容量冠は使いませんでした。これで支障なく各バンド共振調整できます。 なお、HF帯ハイバンドになると無闇にHigh-Qなアンテナにはなりませんからコロナ放電対策は不要でした。 以下、改良後の様子を要約します。

【14MHzのSWR特性】

nanoVNAを使って共振特性を確認します。

写真に14MHzのSWR特性を示します。これは改造後のものです。

改造後のトップセクションはロッド・アンテナです。 伸縮できるので共振周波数の調整範囲はかなり広くなりました。 従ってコイルのタップ調整は多少ラフに行なっても共振周波数をバンド内に持ってくるのは容易でした。

【14MHzの飛びかた】

PSKRで飛びかたを確認しました。 パソコンの画面をキャプチャしたものです。

既にご存知かも知れませんがPSKRの概略をあらためて説明しておきます。

最近はやりのFT-8のようなデジタルモードではパソコンを使ってオンジエアします。パソコンにはJTDXやWSJT-Xと言った専用アプリを走らせます。

専用アプリには受信時に聞こえた(見えた)ステーションの情報をサーバにアップロードする機能があります。もちろんパソコンはインターネットに常時接続されているのが前提です。 その上がってきた各局からの受信情報をまとめて表示するサイトがPSKRです。 PSKR(←リンク)をアクセスすると自局電波が世界中のどこで受信されたのか良くわかります。初めてPSKRを開いた際には自局コールサイン、運用バンド、モードなど必要な情報を設定して表示させます。(左の画面)

吹き出しに「XX min」と表示のあるのがレポートをサーバーに上げてくれた受信局です。例として44minとあるのはこの画面キャプチャの44分前に見えたという意味です。そこへマウス・カーソルを当てればその受信局の詳細情報が表示できます。

これは2024年1月28日の16:30(JST)ころ14MHz/20m Bandにオンジエアした際の伝搬状況です。送信電力は50WでアンテナはこのDuo-Band Whipです。 アンテナのテストを兼ねたPOTA活の一環として訪れた上武県立自然公園内:児玉千本桜堤付近からオンジエアです。運用した頃は冬なので誰もいませんでしたが桜の名所ですから開花が遅れた今年は丁度いま賑わってます。(埼玉県本庄市児玉町高柳・GL:PM96ne、標高:約120m) 県道沿いで行くには便利な場所ですが特に無線に向いたロケーションとは思えません。 HF帯は電離層反射なので良いとして、V/Uの移動運用にはむしろ不向きでしょう。

流石に14MHz/20m BandはDXバンドだけあって海外へよく飛んでます。 但し夜間帯を通るパスはないらしく北米は良くありません。 昼間〜夕方ゾーンのアジア・オセアニアと東欧が良いです。夏季で日照時間が長い南米にも飛んでます。 このオンジエアではアルゼンチン:LU2やインドネシア:YC2とできたほか中国、韓国とは複数局と交信できました。 日本国内もわりあいスキップせず満遍なく飛ぶ感じです。

SWR特性だけでは良し悪しはわかりませんが電波の飛び具合を見るとまずまず良好なアンテナと言えそうです。

【18MHzのSWR特性】

同じくnanoVNAを使って共振特性を確認します。

写真に18MHzのSWR特性を示します。こちらも改造後のものです。

バンドの切り替えはコイルのタップ位置を変えているだけです。 具体的にはコイルのタップをミノムシ・クリップで挟んで切り替えています。 そのあと先端部分の伸縮で共振周波数を微調整します。 運用中、心配していたタップ切り替えによる不安定さのようなものは感じませんでした。 SWR値も常に安定していたので問題はないようです。

【18MHzの飛びかた】

同じくPSKRで飛びかたを確認しました。 パソコンの画面をキャプチャしたものです。

移動地、パワーなどは上記20mバンドと同じです。 この18MHz/17m Bandもサンスポットの極大期にはDXingに向いたバンドです。 新しくできたWARCバンドなのでオンエア局数は20m Bandより少なめです。18MHz帯は3級局から出られます。

やはり夜間帯を通るパスはないようで、北米はダメですが日照のあるゾーンへ良く飛んでます。アジア・オセアニアが良好です。 QSOできるかどうかは別としても(笑)カリブ海からもレポート上がっています。 Euも20m Bandよりも深い方(西方向へ)開けています。 実際にスペイン: EA局に呼んでもらったのですが、QRMで尻キレてしまいました。(ちょっと残念) 30分程度のオンジエアでしたが、オーストラリア:VKや西マレーシア:9WとQSOできました。中距離の中国・韓国局は国内なみに交信できます。 逆に日本国内近距離はスキップするかと思ったのですがマズマズ満遍なく飛ぶようでした。打ち上げ角の関係でしょうか。

このバンドも飛び具合から見て十分使えるアンテナと言えるでしょう。 波長が短くなった分だけ幾らか輻射効率もアップしているはずです。

☆

輻射効率が悪くて一時はどうしようか迷ったアンテナですが、原因究明と対策ができ使い物になるアンテナとして蘇りました。飛び具合も悪くないので及第点でしょう。

これは当然でしょうが、いずれのバンドも地上高があるホーム・シャックのビームアンテナと比べたらだいぶ心細さを感じました。 しかし条件の悪い移動運用ですからこんなものなのでしょう。給電点の地上高は1.5mで長さも僅か2mにも満たない小さなアンテナです。

移動運用でこれ以上を望むなら高さのあるフルサイズのDPアンテナや或いはビームアンテナを架設すると言った大掛かりな運用になるでしょう。 それは私が目ざす「お手軽移動運用」とはまた別の世界です。(笑)

【IC-7300とFC-700】

IC-7300を使っていて内蔵オート・アンテナ・チューナの整合範囲が狭いと感じることがあります。

小型の筐体にオールバンドSSBトランシーバの機能を全て搭載しアンテナチューナ(ATU)まで内蔵しているのですから限界があってしかるべきでしょう。コンパクトで良くできたトランシーバだと思っています。

外付けのリモート・アンテナ・チューナも用意されています。メーカーとしては内臓ATUでダメならそれを買って欲しい訳でしょう。w

試したところ整合状態が厳しい時は外付けチューナを使うと良さそうでした。 お手軽移動運用の趣旨から言って機材が増えるのは好ましくありませんがRigの性能がフルに発揮できないのではやむを得ません。状況によって外付けチューナを使うことも考えましょう。これで整合の難しさはほとんど解消できます。

☆

ステンレス製のアンテナロッドがローディング・コイルに影響を与え、アンテナの輻射効率を低下させると言う話でした。 原因がわかれば対策が考えられます。 構造を変えるのではなく素材を変えて解決できました。

真鍮なら大丈夫でステンレス鋼が良くないのは電気抵抗の違いにあると思います。あまり気にされないかもしれませんがステンレス材の電気抵抗値はかなり大きいのです。錆びなくて安価なことからステンレス線をダイポール・アンテナに使うHAMもあるそうですが、いちど抵抗値を計ってみると面白いでしょう。 意外に抵抗値が大きくて驚くはずです。 まあロスを気にしなければアンテナのQが下がって広帯域特性になるのでステンレス線のDP-ANTもFBと言えるかもしれませんが・・・私は使いませんけど。(笑)

コイルで発生した磁束により周辺に存在する金属には誘導電流を生じます。その生じた誘導電流によっても磁界が発生しエネルギーとしては消費されることなく殆どが戻ってくるでしょう。 しかしステンレス材のように電気抵抗が大きかったら自身の電気抵抗でIR損失が発生し熱になってしまい全部は戻ってきません。 簡単に考えるとこのような理由でステンレス材がコイル近傍にあるとロスになるのでしょう。 磁束の外にあれば問題ないわけで要は使い方かもしれませんが。 そして磁束が閉じ込められ外に漏れないトロイダル・コイルをもしも使っていたなら現象に遭遇することはなかったかも知れませんね。

☆ ☆ ☆

モバイルでオンジエアのお話はアンテナ基台から始まり磁石アース板の効果を6mアンテナで確かめたあと、いよいよ本題のHF帯アンテナの製作へと進みました。 10MHz、7MHzと作って実用的な成績が得られました。 続いて14/18MHzのDuo-Band ANTでは少々躓きましたが解決できてマズマズの成績を得ました。 交信実績のなかった6mも近所の空き地でテストしたらVK4とQSOできたので、これからPOTAの運用も楽しみです。 まだ残ったHF帯HAMバンドもありますがアンテナ製作とモバイルのお話は一旦おしまいにします。バンドが追加できたら改めて紹介しましょう。

車載アンテナは「システム」であってホイップ・アンテナ単体では完結できないことを実感しました。 伏線ではありませんが各回のBlogテーマはどれも関連づけて回収できたと思っています。 ここを見ているのは電子部品や回路趣味のお方が殆どでしょうから興味の範囲外だったかも知れません。 しかし無線通信はアンテナがあってこそ成り立つものです。いくら優秀な通信機と言えどもPoorなアンテナでは本領は発揮し得ません。 移動運用ともなるとさらに固有の難しさも表面化してきます。 少しだけでも興味を持ってお付き合い頂けたようでしたら幸いです。

最近は自作したアンテナであちこちの公園移動運用(POTA)を楽しんでいます。 カミさんと出かけることも多くて私は無線であちらは公園の散歩や散策を楽しんでいます。 だいたい1時間を目処にしていて、あまり長時間オンジエアすることはないので、お互いに飽きずに楽しめる程よいレクレーションになっています。 せっかく訪れた公園です。いくらか健康に良いように私も散策してから帰ることにしています。 ではまた。 de JA9TTT/1

(おわり)nm

abstract

I built a duo-band antenna for 14 MHz and 18 MHz. But the performance of that antenna was poor. The RF Power radiation efficiency was not good. The reason was the stainless steel antenna element. The antenna was a shortened version with a loading coil. The presence of stainless steel in the magnetic field of the coil caused a loss of RF power. I was able to improve the situation by dropping the stainless steel material and replacing it with brass material. I would not have experienced this if I had used toroidal coils instead of air-core coils. However, toroidal coils have other problems. (2024.04.09 de JA9TTT/1 Takahiro Kato)

【昔っから言いますが・・】

HF帯(短波帯)のモバイル用ホイップ・アンテナの話題が続きます。 そもそもHF帯でモバイル運用したいなんて言う物好きなHAMは稀でしょうから、そんなアンテナの話は飽きてきたのではありませんか? 前回の7MHz用でおしまいにしようと思ってました。

今回は14MHzと18MHzの2バンド用アンテナを作りますが、それを紹介するのは主だった目的ではないのです。

残念ながらはじめに作ったものは低性能なアンテナになりました。 何でも成功する訳じゃありません。むしろ「失敗作」と言って良いでしょう。 なぜなのかしばらく悩んだのですが、むかし聞いたことのある話を思い出したのです。自分の経験ではないのでうろ覚えでしたがそれを切っ掛けに解決することができました。 ・・・どうやら成功の元になったようです。

☆

私自身では面白い経験だったのですが大抵のお方にとっては何か意味があるとも思えません。 いつ何をやったらどうなったのかと言う自身の備忘が主目的です。 モバイルからHFにオンジエアの最終回の話しはあいも変わらず雑談チックになりますが悪しからず。 この先はお薦めもしませんので、もしお暇でもあったら眺めてみて下さい。 暇つぶしくらいにはなるでしょう。(ココを見てる時点であなたは暇人ですが・笑)

ー・・・ー

【トロイダル・コイルは】

最初の写真はトロイダル・コイルですがこの先の話には出てきません。トロイダル・コイルで短縮アンテナの「ローディング・コイルを」と目論んでました。High-Qという先入観からです。

結論としてトロイダル・コイルは周波数特性が悪く不適当でした。特定の周波数範囲ではかなりHigh-Qですが空芯コイルと比べ高いQが保てる周波数範囲はずっと狭いのです。

条件に合う単一バンドの短縮アンテナならある程度使える可能性はあります。しかし複数のHAMバンドにまたがるアンテナには向きません。

またHigh-Qとは言っても最適化された空芯コイルを凌駕するほどの性能は難しそうです。 磁気コアによる鉄損や磁束飽和の観点から言っても短縮アンテナには空芯コイルが無難だと言う結論です。 トロイダル・コイルは回路用部品であってこうした短縮アンテナ用ではないようです。(私見です)

【移動式容量冠】

HF帯ハイバンド・・・14MHz以上のHAMバンドへオンジエアしたいと思いました。

2024年は黒点周期:サイクル25の極大期にあたります。極大期にはHF帯のハイバンドが活性化します。 まさしくDXingのチャンスです。

チャンスを逃すのは惜しいです。11年後のサイクル26は生きてないかも知れません。 POTAなどのモバイルでもオンジエアが楽しめるようにHF帯ハイバンドの移動用アンテナを作ってみます。

☆

ところが手持ち部材が底を突いてきました。買わずに済ませるには工夫が必要でした。

今回もセンタ・ローディング形式で作りましょう。 7MHzのアンテナ製作のとき切り残ったグラスファイバ・ロッドを使います。そのため全体に細くてコイルの下部セクションとしては少々貧弱です。できたらもっと長さも欲しいところです。 しかし波長は20mあるいは17mとLow-Bandよりずっと短いので何とかなるでしょう。軽量に作れば強度も大丈夫そうです。

使うことにしたグラスファイバ・ロッドは先端が細いため前作のような方法でロッド・アンテナを繋ぐことはできません。 そこで持っていたステンレス(SUS)製のロッド(φ3mmの棒)を上部エレメントとして使いました。長さは820mmあります。もともとグラスファイバ・ロッドの先端に付けるための部材でした。アンテナ用として先端に金属球も付いてます。

しかしこれを使うと上部セクションの長さを加減できないのが大きな問題でした。コイルのタップ切換だけで共振周波数をシビアに追い込むのは難しいからです。

写真は共振周波数を微調整するのための移動式の容量冠(キャパシティ・ハット)です。 ミノムシ・クリップで挟む位置をスライドして共振点を微調整します。思っていたよりも調整可能な周波数範囲が狭いのはやや不満でしたが試行錯誤を繰り返してある程度うまく行きました。

【タップ式コイル】

2バンドアンテナはローディング・コイルのタップ切換えで実現します。 ほかにトラップ式で作る高級な方法もありますが初期調整はかなりの困難が予想されます。

運用時のバンド切替えは少々面倒くさいですがタップ選択式を採用しました。 ミノムシ・クリップによるタップ切替えには幾分不安を感じます。 ただしコイルより先の部分はRF電流が少なくなるので旨くタップを引き出せば何とかなるでしょう。

こんどはバンドチェンジのたびにコイル容器を開閉します。この保護容器は開閉が容易なのは好都合でした。

【14MHz and 18MHz Whip Antenna】

下部セクションが細くて華奢な感じがします。しかし走行しながらの運用はしないので折れることはないでしょう。

全体的に軽量にできたのでアンテア基台の負担が少ないのはFBです。 流石に3つ目ともなれば目新しさはぜんぜん感じませんがマズマズの出来映えです。(・・・と自画自賛・笑)

家人には「同じのを3つも作ってどうするの?」なんて言われてしまいました。 確かに同じにしか見えないかな。(笑)

【残念ですが解体します】

何が問題かといえば送信時のロスが大きいことです。ローディング・コイルのあたりで発熱がありどうも輻射効率が低いようなのです。

見ての通り過去2作とほとんど違わず何が原因なのか悩みました。 結論から述べてしまうとステンレス・ロッドがコイル内に掛かっていることが損失発生の原因でした。 原因がわかれば対策しなくてはなりません・・・。

思い出したのはずいぶん前の話です。さるHAM局がモバイル用アンテナを作ったそうですが飛びが悪いと言うのです。細かい症状は忘れましたがコイル部分にかなりの発熱があるとのこと。そして輻射エレメントにステンレス材を使ったセンター・ローディング形式らしかったのです。

その時は構造など詳しくお聞きした覚えがあります。ただ、私には何が原因なのかすぐには思い浮かびませんでした。 あとでそのアンテナを良く見せてもらう機会があったのですが器用なお方らしく丁寧にそして見栄えも良く美しく仕上げてあったことを思い出します。

その後どうなったか記憶にないので、そのHAM局は諦めてしまったのかもしれません。 そして今回は私がよく似た現象に遭遇した訳です。 以下は問題検証の様子です。

【ローディング・コイルのQ】

アンテナ製作に使っているコイルは実績のあるものです。

念のために改めて確認していますが、写真のようにQu=265くらいあります。(巻数が少なく周波数が高いのでややQが低下)

巻き数や測定周波数によって変化しますが、だいたい300前後が得られます。エアダックス・コイルとして正常でしょう。

【ロッド・アンテナをコイルに挿入】

従来の構造である、ロッド・アンテナがコイルの端部に掛かった(挿入された)状態を再現してみます。

少しインダクタンスの変化とQの減少が認められます。ただしQu=225くらいあるのでそれほど大きな減少ではありませんでした。もっと低下するかと思っていたので意外でした。

そういえば、コイルのインダクタンス調整に真鍮コアを使うと言う話を思い出しました。FMやTVのチューナと言ったVHF帯のコイルのインダクタンス調整に使っているとのこと。 Qの低下を来さずにインダクタンスを加減する(減らす)ことができるので使っているのでしょう。

使っている伸縮式ロッド・アンテナ(6段式)は真鍮にクロームメッキしたパイプが使われています。 そのためQの低下をあまり来さずに済んでいるのでしょう。

【ステンレス・ロッドでQ低下】

今度は実際にアンテナに使ったステンレス・ロッドをコイル端部に挿入してみました。

幾らかインダクタンスも変化しますが、それ以上にQuの低下が顕著です。 約半分のQu=130になってしまうのです。

265だったQuが半分以下になったら損失は倍増です。 そうでなくてもローディング・コイルにはロスがあるのに損失が2倍になったら電波の飛びが悪くなって当然ですね。

アンテナの部材としてステンレス材は悪くはないと思っています。しかし使い方を考えないと性能低下をきたすことがあるのです。良い勉強になりました。

☆

ステンレス製の上部セクションを真鍮製のロッド・アンテナに交換することで対策しました。 実績のある方法へ戻ったわけです。 使っているグラスファイバ・ロッドの先端部は細いので、その先に付けるロッド・アンテナとの結合方法を考える必要がありました。これにはアクリル樹脂製のパイプに両方を挿入する形式で接続しています。

アンテナの上部セクションが伸縮可能になったので移動式の容量冠(キャパシティ・ハット)はやめました。 また波長で考えて上部セクションの長さは十分に得られているので容量冠は使いませんでした。これで支障なく各バンド共振調整できます。 なお、HF帯ハイバンドになると無闇にHigh-Qなアンテナにはなりませんからコロナ放電対策は不要でした。 以下、改良後の様子を要約します。

【14MHzのSWR特性】

nanoVNAを使って共振特性を確認します。

写真に14MHzのSWR特性を示します。これは改造後のものです。

改造後のトップセクションはロッド・アンテナです。 伸縮できるので共振周波数の調整範囲はかなり広くなりました。 従ってコイルのタップ調整は多少ラフに行なっても共振周波数をバンド内に持ってくるのは容易でした。

【14MHzの飛びかた】

PSKRで飛びかたを確認しました。 パソコンの画面をキャプチャしたものです。

既にご存知かも知れませんがPSKRの概略をあらためて説明しておきます。

最近はやりのFT-8のようなデジタルモードではパソコンを使ってオンジエアします。パソコンにはJTDXやWSJT-Xと言った専用アプリを走らせます。

専用アプリには受信時に聞こえた(見えた)ステーションの情報をサーバにアップロードする機能があります。もちろんパソコンはインターネットに常時接続されているのが前提です。 その上がってきた各局からの受信情報をまとめて表示するサイトがPSKRです。 PSKR(←リンク)をアクセスすると自局電波が世界中のどこで受信されたのか良くわかります。初めてPSKRを開いた際には自局コールサイン、運用バンド、モードなど必要な情報を設定して表示させます。(左の画面)

吹き出しに「XX min」と表示のあるのがレポートをサーバーに上げてくれた受信局です。例として44minとあるのはこの画面キャプチャの44分前に見えたという意味です。そこへマウス・カーソルを当てればその受信局の詳細情報が表示できます。

これは2024年1月28日の16:30(JST)ころ14MHz/20m Bandにオンジエアした際の伝搬状況です。送信電力は50WでアンテナはこのDuo-Band Whipです。 アンテナのテストを兼ねたPOTA活の一環として訪れた上武県立自然公園内:児玉千本桜堤付近からオンジエアです。運用した頃は冬なので誰もいませんでしたが桜の名所ですから開花が遅れた今年は丁度いま賑わってます。(埼玉県本庄市児玉町高柳・GL:PM96ne、標高:約120m) 県道沿いで行くには便利な場所ですが特に無線に向いたロケーションとは思えません。 HF帯は電離層反射なので良いとして、V/Uの移動運用にはむしろ不向きでしょう。

流石に14MHz/20m BandはDXバンドだけあって海外へよく飛んでます。 但し夜間帯を通るパスはないらしく北米は良くありません。 昼間〜夕方ゾーンのアジア・オセアニアと東欧が良いです。夏季で日照時間が長い南米にも飛んでます。 このオンジエアではアルゼンチン:LU2やインドネシア:YC2とできたほか中国、韓国とは複数局と交信できました。 日本国内もわりあいスキップせず満遍なく飛ぶ感じです。

SWR特性だけでは良し悪しはわかりませんが電波の飛び具合を見るとまずまず良好なアンテナと言えそうです。

【18MHzのSWR特性】

同じくnanoVNAを使って共振特性を確認します。

写真に18MHzのSWR特性を示します。こちらも改造後のものです。

バンドの切り替えはコイルのタップ位置を変えているだけです。 具体的にはコイルのタップをミノムシ・クリップで挟んで切り替えています。 そのあと先端部分の伸縮で共振周波数を微調整します。 運用中、心配していたタップ切り替えによる不安定さのようなものは感じませんでした。 SWR値も常に安定していたので問題はないようです。

【18MHzの飛びかた】

同じくPSKRで飛びかたを確認しました。 パソコンの画面をキャプチャしたものです。

移動地、パワーなどは上記20mバンドと同じです。 この18MHz/17m Bandもサンスポットの極大期にはDXingに向いたバンドです。 新しくできたWARCバンドなのでオンエア局数は20m Bandより少なめです。18MHz帯は3級局から出られます。

やはり夜間帯を通るパスはないようで、北米はダメですが日照のあるゾーンへ良く飛んでます。アジア・オセアニアが良好です。 QSOできるかどうかは別としても(笑)カリブ海からもレポート上がっています。 Euも20m Bandよりも深い方(西方向へ)開けています。 実際にスペイン: EA局に呼んでもらったのですが、QRMで尻キレてしまいました。(ちょっと残念) 30分程度のオンジエアでしたが、オーストラリア:VKや西マレーシア:9WとQSOできました。中距離の中国・韓国局は国内なみに交信できます。 逆に日本国内近距離はスキップするかと思ったのですがマズマズ満遍なく飛ぶようでした。打ち上げ角の関係でしょうか。

このバンドも飛び具合から見て十分使えるアンテナと言えるでしょう。 波長が短くなった分だけ幾らか輻射効率もアップしているはずです。

☆

輻射効率が悪くて一時はどうしようか迷ったアンテナですが、原因究明と対策ができ使い物になるアンテナとして蘇りました。飛び具合も悪くないので及第点でしょう。

これは当然でしょうが、いずれのバンドも地上高があるホーム・シャックのビームアンテナと比べたらだいぶ心細さを感じました。 しかし条件の悪い移動運用ですからこんなものなのでしょう。給電点の地上高は1.5mで長さも僅か2mにも満たない小さなアンテナです。

移動運用でこれ以上を望むなら高さのあるフルサイズのDPアンテナや或いはビームアンテナを架設すると言った大掛かりな運用になるでしょう。 それは私が目ざす「お手軽移動運用」とはまた別の世界です。(笑)

【IC-7300とFC-700】

IC-7300を使っていて内蔵オート・アンテナ・チューナの整合範囲が狭いと感じることがあります。

小型の筐体にオールバンドSSBトランシーバの機能を全て搭載しアンテナチューナ(ATU)まで内蔵しているのですから限界があってしかるべきでしょう。コンパクトで良くできたトランシーバだと思っています。

外付けのリモート・アンテナ・チューナも用意されています。メーカーとしては内臓ATUでダメならそれを買って欲しい訳でしょう。w

試したところ整合状態が厳しい時は外付けチューナを使うと良さそうでした。 お手軽移動運用の趣旨から言って機材が増えるのは好ましくありませんがRigの性能がフルに発揮できないのではやむを得ません。状況によって外付けチューナを使うことも考えましょう。これで整合の難しさはほとんど解消できます。

☆

ステンレス製のアンテナロッドがローディング・コイルに影響を与え、アンテナの輻射効率を低下させると言う話でした。 原因がわかれば対策が考えられます。 構造を変えるのではなく素材を変えて解決できました。

真鍮なら大丈夫でステンレス鋼が良くないのは電気抵抗の違いにあると思います。あまり気にされないかもしれませんがステンレス材の電気抵抗値はかなり大きいのです。錆びなくて安価なことからステンレス線をダイポール・アンテナに使うHAMもあるそうですが、いちど抵抗値を計ってみると面白いでしょう。 意外に抵抗値が大きくて驚くはずです。 まあロスを気にしなければアンテナのQが下がって広帯域特性になるのでステンレス線のDP-ANTもFBと言えるかもしれませんが・・・私は使いませんけど。(笑)

コイルで発生した磁束により周辺に存在する金属には誘導電流を生じます。その生じた誘導電流によっても磁界が発生しエネルギーとしては消費されることなく殆どが戻ってくるでしょう。 しかしステンレス材のように電気抵抗が大きかったら自身の電気抵抗でIR損失が発生し熱になってしまい全部は戻ってきません。 簡単に考えるとこのような理由でステンレス材がコイル近傍にあるとロスになるのでしょう。 磁束の外にあれば問題ないわけで要は使い方かもしれませんが。 そして磁束が閉じ込められ外に漏れないトロイダル・コイルをもしも使っていたなら現象に遭遇することはなかったかも知れませんね。

☆ ☆ ☆

モバイルでオンジエアのお話はアンテナ基台から始まり磁石アース板の効果を6mアンテナで確かめたあと、いよいよ本題のHF帯アンテナの製作へと進みました。 10MHz、7MHzと作って実用的な成績が得られました。 続いて14/18MHzのDuo-Band ANTでは少々躓きましたが解決できてマズマズの成績を得ました。 交信実績のなかった6mも近所の空き地でテストしたらVK4とQSOできたので、これからPOTAの運用も楽しみです。 まだ残ったHF帯HAMバンドもありますがアンテナ製作とモバイルのお話は一旦おしまいにします。バンドが追加できたら改めて紹介しましょう。

車載アンテナは「システム」であってホイップ・アンテナ単体では完結できないことを実感しました。 伏線ではありませんが各回のBlogテーマはどれも関連づけて回収できたと思っています。 ここを見ているのは電子部品や回路趣味のお方が殆どでしょうから興味の範囲外だったかも知れません。 しかし無線通信はアンテナがあってこそ成り立つものです。いくら優秀な通信機と言えどもPoorなアンテナでは本領は発揮し得ません。 移動運用ともなるとさらに固有の難しさも表面化してきます。 少しだけでも興味を持ってお付き合い頂けたようでしたら幸いです。

最近は自作したアンテナであちこちの公園移動運用(POTA)を楽しんでいます。 カミさんと出かけることも多くて私は無線であちらは公園の散歩や散策を楽しんでいます。 だいたい1時間を目処にしていて、あまり長時間オンジエアすることはないので、お互いに飽きずに楽しめる程よいレクレーションになっています。 せっかく訪れた公園です。いくらか健康に良いように私も散策してから帰ることにしています。 ではまた。 de JA9TTT/1

(おわり)nm

2024年3月25日月曜日

【Antenna】Making a 40m-Band Whip Antenna

【40mバンドのホイップ・アンテナを作る】

abstract

I have built a 40m Band Whip Antenna. This antenna is designed to enjoy HAM by carrying a radio station in a car and moving it around. This antenna has the same structure as the 30 m band antenna introduced in two previous Blogs. Of course, the resonant frequency is different. The construction was easy as I used some parts specially designed for whip antennas. The finished antenna sounds good and radiates well. (2024.03.25 de JA9TTT/1 Takahiro Kato)

【モバイルアンテナの材料】

40m Band:7MHz帯はHF帯(短波帯)のメインストリートでしょう。ライセンスに関係なく初級局からオンジエアでき国内に満遍なく飛ぶうえ夜間ともなれば海外へも飛んでくれます。それだけに混信も激しいのですがいつも誰かがオンジエアしているので交信相手には事欠きません。

波長:λは40mもあります。 1/4・λでも10mもあってモバイル用のアンテナは超短縮型にならざるを得ません。 それだけに輻射効率の良いアンテナは難しくなるのですが上手に作れば十分楽しめるだけのものができます。

写真は手持ちのアンテナ製作用パーツです。 今回は活用する最後のチャンスと考えて長いこと温存していた専用の部材を投入することにしました。 茶色のパイプ状がグラスファイバ・ロッドで、以前HF帯のモバイル運用が流行ったころヘリカル巻き短縮アンテナの製作によく使われた素材です。 その下がそれに適合するコネクタ部でM型になっています。一番下は6段のロッド・アンテナで30m Bandのホイップ・アンテナに使ったものと同じです。完全に伸ばした全長は101.5cmのものです。 各部材の入手・代替などに関する情報は後ほどあります。

☆

再びモバイル用アンテナ製作の話に戻ります。 30m Bandは楽しいHAMバンドですが30mのアンテナだけではオンジエアの幅が狭くなってしまいます。これから40m Band用のモバイル・ホイップ・アンテナを製作します。やはりHF帯のメインストリートに出たいですね。 FBなアンテナができたならドライブの楽しみも広がります。

製作するアンテナの基本構造はすでに前のBlog(←リンク)で扱った30m Band用と同じセンター・ローディング形式です。 実用的な性能が得られた実績を重視し同じ形式にしました。 もう一つの理由はセンター・ローディング形式なら設計手法が確立しているため試行回数が少なく済むからです。

ヘリカル巻きの短縮型も面白そうに思ったのですが製作経験がないので諦めました。 従って既に前のBlogをご覧でしたらアンテナ形式そのものに目新しさはないでしょう。 しかし、もしお暇ならお付き合いください。 Somithing NEWはあるはずです。

【エア・ダックス・コイルと切断治具】

40m Bnadのホイップ・アンテナでも短縮コイルにエア・ダックスを使います。 コイルはボビン(巻枠)に自分で巻いて作れるパーツですが、手持ちを温存する意味もないので積極的に使うことにします。

型番はNo.401016で30m Bnadのホイップ・アンテナに使ったものと同じです。 流石に太めの線を巻いた空芯コイルだけあってQu=300が得られます。自作すればもう少しHigh-Qなコイルも十分可能なのですがQu=300はけして悪い数字ではありません。かなり良い性能と言えます。 活用することにしました。

エア・ダックスの切断に使えそうなプラスチックス切断用の治具(写真手前)があったので使ってみました。 コイルの「巻き」をあまり無駄にせず綺麗に切断可能ですがそもそもエア・ダックスが手に入らないパーツなので・・・道具もあまり意味はないかも。w

【40m用センタ・ローディングANTの設計】

今回は計算してから製作を始めました。 ただし設計アプリを使うためにはアンテナ・エレメントの寸法が明確でないと始まりません。

具体的にはコイルより下側のベースセクションと上側のトップセクションの寸法です。長さと平均径が必要です。 また容量冠の有無と、もし使う場合はその寸法・構造も必要です。

下部・ベースセクションに使うグラスファイバ・ロッド(上記写真で茶色のパイプ)は、長さ:L=140cm、元口径=1.4cm、先端径=0.55cm、肉厚=1mm程度のものです。ただし細い先端部は使いません。 コイルより上部のトップセクションは伸縮可能なロッド・アンテナ(テレスコーピック・アンテナ)を使います。 従ってグラスファイバ・ロッドは適当な寸法で切断しました。

センタ・ローディング・アンテナの輻射効率はRF電流の腹にあたる下部セクションの影響が大です。 全長を一定とすればRF電流が小さくなるコイルより上部を長くするよりもRF電流が大きい下部セクションを長くした方が有利です。ボトムローディング形式は構造的に有利ですが輻射効率では最低と言えます。 だからと言って短絡的な考えでコイルを最頂部に置くのがベストかと言えば、そうではありませんが・・・。

(参考:簡単に言うと先端に行くほど共振に必要なインダクタンスが増えHigh-Qなコイルの製作・保持が難しくなります。接地抵抗を仮定しローディング・コイルのQをパラメータとして計算すれば最適なコイルの位置が求まります)

種々の要素を検討してグラスファイバ・ロッドは元口から82.5cmのところで切断しました。 ただし一部はコネクタ部とコイルのサポートに取られるので電気的に有効な長さは実測67cmになりました。 上部セクションはロッド・アンテナそのものなので長さ101.5cmありますが、使用時にはやや縮めて使うことを想定し96cmとして計算しています。 先端の容量冠は実際は8の字型ですが等価的に直径8cmの円形でスポークは4本として計算しました。 接地抵抗はとりあえず10Ωとしておきますので効率計算は参考値です。

必要なローディング・コイルのインダクタンスは約42μHと計算されます。エア・ダックス・コイル:No.401016はちょうど40回巻きが必要です。 コイルのバラツキおよび計算誤差などを考慮して数回(3回)多めに切断しておきます。

【ローディング・コイルの調整】

おおよそのインダクタンスは計算で求めてあります。

エアダックス・コイルのインダクタンスは付属のチャートから求められますが、かなりラフなものです。 実際にはQメータで測定してインダクタンスを確認しておきました。(どうせタップで加減するので事前の精密な測定は必要ありません)

上部エレメントからクリップ付きリード線を出しコイルの巻き線を摑んで共振する周波数を探ります。

超短縮なアンテナは狭帯域になりがちです。SWRが下がり実用となるのは共振周波数付近の狭い範囲になります。ほぼスポット周波数と言えます。正確に7050kHzあたりで共振するようコイルを調整しました。 実際に使用する際は上部のロッド・アンテナ部分を伸縮させてオンジエアする周波数にぴったり合うようシビアに加減する必要があります。 もしもブロードな周波数特性を示すならその短縮アンテナの輻射効率はかなり低い可能性があります。これはご参考までに。

コイルの調整に際してロッド・アンテナの長さは±に調整できるよう適度に縮めた状態で行ないます。 伸ばし切った状態で決めたら共振周波数を低い方へ調整できません。

【ケースを被せてローディング・コイル完成】

防水・防滴構造ではありませんが多少の天候変化なら大丈夫なようにしておきます。

コイル全体をプラスチックス製のケースに収納してあります。 このケースは200mlのサンプル容器というものです。 蓋の部分を下にして逆さまに使っています。ローディング・コイルは蓋の部分に固定されています。

容器は適当な寸法の手持ちがあったので使いましたが100均で様々なものが手に入るので適当なものを見つければ良いでしょう。なお金属製の容器はインダクタンスやQへの影響が大きいため使うべきではありません。

もし走行しながら使えるアンテナを作りたいなら十分な検討が必要です。 破損がないように構造や部材を吟味しなくてはならないでしょう。

このアンテナは車をどこかに停めて半固定でのオンジエアで使うことを前提に考えています。移動運用地に到着してからアンテナ基台に装着します。 着脱で簡単に壊れないよう相応の機械的な強度は考えていますが停車した状態で使うべきでしょう。 アンテナ基台もそれほど大型ではありませんから車体への固定が十分に強固とは思えません。ある程度可能かもしれませんが大きめのアンテナを付けたままの走行は安全ではないでしょう。

【コイルは発熱する】

コイルのQが無限大でない限り必ずロスが発生します。5Wと言ったQRPなら発熱量はたかが知れていますが移動局の限度いっぱいの50Wも出すと馬鹿にできません。

このアンテナの場合、入力電力の約35%がコイルで熱になる計算です。Qu=300というかなり良いコイルを使っていてもそれだけのロスが発生します。 例えば送信電力:50Wとしてコイルでの損失は18Wくらいになります。これは無視できない発熱量です。

テストの段階で連続的な送信を行なったところ「共振周波数の跳躍」が見られました。 約30kHzほど上昇したのです。温度上昇によって製作時の機械的なストレスが解放されたものと考えられます。 その後は50Wでのオンジエアでも変化を感じないので安定したようです。

【インピーダンス・マッチング】

C-L型のインピーダンスマッチング回路を付けました。

この部分も30m Bandのホイップ・アンテナと同様の構造です。ただし容量値は異なります。

給電点のインピーダンスを想定して計算すると、必要な容量値は約610pFになりす。計算自体がアバウトなものですから680pFのディップド・マイカ・コンデンサで間に合わせました。 マッチング回路のインダクタンスは約0.54μHでローディング・コイルに含めることで省略できます。

写真でアンテナ下部の構造がわかると思います。グラスファイバ・ロッドは同軸ケーブル(10D-2V)を剥いて作った網線で覆われています。

これは下部エレメントを低抵抗に作ってロスを減らし、しかも太くすることで静電容量を大きくする目的があります。 アンテナのキャパシティをできるだけ大きくすることで、なるべく少ないインダクタンスのローディング・コイルで共振させるようにします。

もちろん銅の網線が裸のままでは錆びてくるのでテープを巻いておきます。ビニル・テープなどではなくて自己融着テープが最適です。自己融着テープは高周波的な特性も悪くありません。自己融着テープも最近はホームセンターの電材コーナーに置いてあります。 もし手に入れば太い熱収縮チューブを使うと体裁よく仕上がります。

【マッチング部の防水】

マッチング回路のコンデンサを含めてテーピングしておきます。これでコンデンサが取れてしまうことも防げます。

この部分で意外に厄介なのはコネクタ部とのハンダ付けです。 コネクタ部分はクロームメッキされていて、普通のハンダ付けができないからです。これはコイルより上部のロッド・アンテナ部分も同じです。

ホームセンターへ行くとホワイト・メタル用と言うフラックスが見つかります。是非ともそれを使ってハンダ付けすべきです。

メッキを剥がす方法もありますが材質によっては母材にハンダ付けできないことがあります。 機械的にカシメても良いので確実な接続ができるようにします。高周波回路は接触不良を嫌いますから効率低下が起こらぬようにしたいものです。

(注意:フラックスは酸化性が強いので残存していると錆が出ます。十分な洗浄を!)

【10MHzと7MHzのWhip Antenna】

完成した7MHzのアンテナを並べてみました。左が先に作った10MHzで右が7MHzです。 基本的に同じ構造ですので良く似ています。

写真ではわかりませんが後から作った7MHzは改良された箇所がたくさんあります。 やはり2つ目の製作ともなると最初の経験が活きてきます。 部材も残り物の間に合わせから専用品に代わった部分もあって作りやすさにも違いがありました。

ローディング・コイルのサポート構造は特に進歩した部分です。 10MHz用は主要部分をエポキシ系の接着剤(アラルダイト・ラピッド)で固定し、材質的にエポキシ系で無理があった所をセメダイン・スーパーXという万能接着剤で固定していました。全面的に接着剤に頼る方法です。 7MHz用ではエアダックス・コイルの構造に着目し蓋の部分に樹脂のセパレータ(4本)に合わせた穴加工を行なって固定しました。接着剤は要所に必要最低限だけです。機械的な強度はずいぶん向上し、見た感じも良くなっています。

まったく異なるタイプのアンテナを作ったほうが自作としては面白いのですが、同じ構造なら製作経験を活かすことができ改良に繋がります。実用品を作るという趣旨から言えば悪くない選択だったのではないでしょうか。

【車載した様子】

写真は車載した様子です。コイルより下部のベースセクションが長くなったため10MHzにも増して印象的になりました。

全長は約182cmあります。 装着して走行することはないので支障はないと思います。 コネクタ部分が専用品になったのでベース部分の機械的な強度はずいぶん向上したと感じます。 長くはなっても安心感はアップしています。

写真では見えにくいですが頂部に8の字型のキャパシティ・ハット(容量冠)が付いているのも10MHzのホイップANTに同じです。

【磁石アース板】

周波数が低くなったことからボディーとの結合容量の不足が気になりました。 写真のように小型版(強磁力の方)を2枚使って調整していたのですが、A4版の大きい方を追加してみました。

多少の変化は見られますが大きな違いはないことがわかったので現在は写真の状態で実用しています。 もちろん磁石アース板なしでは不安定なうえ調整も狂ってしまいまったくダメです。(笑)

【7MHz Whip Antennaの共振特性】

写真はnanoVNAで観測した7MHzホイップ・アンテナのSWR特性です。7.0MHzを中心に±500kHzの範囲で観測しています。

写真を見ますとSWRが低くくて使用可能な周波数帯域幅はたいへん狭くなっています。 スポット的と言っても良いでしょう。 高い輻射効率を狙ってできるだけロスを減らした短縮アンテナはかなりHigh-Qになります。 そのため実質的に共振周波数付近のごく狭い周波数範囲でしかオンジエアできません。

FT-8やJT-65(廃れましたが・笑)のようにスポット周波数で運用するモードなら運用中の支障はまったくありません。 CWの場合はCWバンドの低端と高端ではかなり離れているため運用周波数に合わせてアンテナ先端の伸縮により微調整する必要があるでしょう。 同様にSSBでも実際に使う周波数に応じた微調整を行なえば良好な輻射効率でオンジエアできます。

全長は約182cmと10MHz版より30cmくらい長くなっていますが、1/4・λに対する短縮率は約83%と(=17%の長さしかない)むしろ「小さなアンテナ」になっています。そのため輻射効率も少し低下しています。これが現実的なサイズなのでやむを得ないと思います。 あとはうまく電波が飛んでくれたら良いのですが・・・

帯域幅が狭く効率も低いのは超短縮アンテナにならざるを得ないHF帯移動運用の宿命と言えます。 こんなことを書くと混乱するかもしれませんが「アンテナのQは低いほどFB」なのです。しかし損失が大きくなるような方法でLow-Qにしたのでは意味がありませんけれど・・・。おわかりでしょうか?(笑)

【テスト・オンジエアの様子:FT-8】

近くの空き地で移動運用のテスト・オンジエアです。 何かあってもシャックにすぐ戻れるごく短距離の移動です。

共振周波数の調整がやや甘かったのですが、まずまず良く飛んでくれました。

CQを出したところ数局に呼んでいただけました。 コンデイションの影響もあるとは思いますが、約83%短縮という超短縮アンテナでも十分な実用性能が得られています。見かけスマートな市販ANTよりも効率はずいぶんマシでしょう。

移動運用には様々なスタイルがあります。ポータブルなQRP機を持ってフィールドに出かけて波を出すのは楽しいものです。私もFT-817なら持ってます。 しかし弱すぎる波では交信相手はだいぶ苦労するでしょう。 私の希みは:たとえ移動運用の貧弱な設備ではあってもできるだけ良い波を出したいのです。 なるべく楽に交信して頂きたいと思っています。 ですからあえてQRPには拘らず事情が許せば法定内で可能なだけのパワーを出しアンテナ系の輻射効率も極力高くありたいのです。 アマ無線は交信できてこそ無線通信です。せっかく出かけた移動運用がボウズじゃ悲しいじゃありませんか。hi

参考:QRPpでkm/Wを競うにはPOTAではなくSOTAが向いています。V/UHFなら標高で飛距離を稼ぐことができるからです。短縮なしフルサイズのアンテナやビームアンテナも使えます。HF帯よりノイズや混信が少ないのも有利です。

【PSKRでも飛びを確認】

トランシーバの受信感度には20dB(電圧で10倍、電力で言えば100倍)以上の余裕があってかなり低効率なアンテナでもよく聞こえるのが当たり前になっています。そうでないと耳の悪いトランシーバと言われてしまいます。w

しかし送信で20dBの余裕は容易ではありません。アンテナのロスを見込んで100倍のパワーに・・・など非現実的です。アンテナの数%の効率の違いに拘るのはそのためです。その数%が飛びには大いに影響します。

そのアンテナを繋いでみたらよく聞こえるからと言って、それはまったくの気休めに過ぎないかも知れません。本当のことは送信した時にわかります。

飛び具合の確認のために7041kHzでオンジエア・テストしてみました。 7041kHz/FT-8は基本的にJA局のみがオンジエアしています。 これはバンド使用区分からやむなくそうなったものと承知しています。

従って受信レポートは海外局からは得られません。 たまたま韓国に1局だけ7041kHzをワッチしていた局がいたようです。 他の日のテストでも国内各局にまんべんなく飛んでくれたのでこのアンテナはかなり旨くいったと言えるでしょう。 もちろん短縮なし・フルサイズの固定局のアンテナと比べちゃいけませんけどね。(笑)

こんどは夜間のDXタイムを選んで7074kHz/FT-8でテストしたいと思います。果たしてどれくらい飛んでくれるでしょうか。(現在は7074kHzで国内局を呼ぶことも可となりましたが、JAどうしの交信は7041kHzがメジャーなようです。DXerには有難いことです)

☆

似たようなアンテナを作るだけですから作るつもりのない人には面白味に欠けたBlogだったでしょう。 寸法図など諸元は省略しましたが、もし参考資料としてご入用でしたら連絡いただけたらと思います。 逆に本当に作ってみたいお方にとってはまだまだ情報不足を感じるはずです。

わからない部分は具体的にお尋ねになってください。私のわかる範囲で返信差し上げます。 製作工程を一からすべて教えろとか、費用を出すから代わりに同じものを作ってくれ等のご要望には応じかねます。 製作例は参考に過ぎないので、あとはみずからも考え、工夫し、手を動かし、完成させてください。 きっと旨く行きます。(笑)

調べてみて驚いたのですが、このアンテナ製作で使ったグラスファイバ・ロッドとそれ専用のM型コネクタ部は現在でも入手可能でした。製作に使ったものは25年以上も前に手に入れたものだったからです。

先端部のロッド・アンテナは昔HAMフェアで購入したもので同じものの入手は難しいかも知れません。 6段式で伸ばした全長は101.5cm(ネジ部含む)、収縮時の長さは20.3cmです。元部分の太さは7mmあります。 長さは少々違っても支障ありません。コイルのタップ位置をわずかに動かせば共振できます。 上記の寸法にこだわることなくネット通販など手に入り易いものを使いましょう。3段式で50cm程度の物でも十分です。

エア・ダックス・コイルの代用は幾らでも可能です。 塩ビやアクリル樹脂のパイプに巻いて所定のインダクタンスが得られるように作ればOKです。 理想を言えば内径85mmのボビンにφ1.6mmの巻線を巻き幅60mm(ピッチ約2.9mm)で22回巻くとHigh-Qなコイルが作れます。さらに2〜3回余分に巻いて調整の余裕を持たせます。 密着巻きではなく必ずスペース巻きで作ります。 密着巻きでは巻線相互の「近接効果」のためQが上がりません。(重要なノウハウ・笑)

写真は「さきたま古墳公園」(埼玉県行田市:POTA JP-1178/JCC-1306)でオンジエアした際のものです。 自作した7MHzホイップ・アンテナは各地のPOTA運用(←リンク)で存分に活躍してくれています。 たくさんのQSOありがとうございます! ではまたどこかの公園から。 de JA9TTT/1

(つづく)fm

abstract

I have built a 40m Band Whip Antenna. This antenna is designed to enjoy HAM by carrying a radio station in a car and moving it around. This antenna has the same structure as the 30 m band antenna introduced in two previous Blogs. Of course, the resonant frequency is different. The construction was easy as I used some parts specially designed for whip antennas. The finished antenna sounds good and radiates well. (2024.03.25 de JA9TTT/1 Takahiro Kato)

【モバイルアンテナの材料】

40m Band:7MHz帯はHF帯(短波帯)のメインストリートでしょう。ライセンスに関係なく初級局からオンジエアでき国内に満遍なく飛ぶうえ夜間ともなれば海外へも飛んでくれます。それだけに混信も激しいのですがいつも誰かがオンジエアしているので交信相手には事欠きません。

波長:λは40mもあります。 1/4・λでも10mもあってモバイル用のアンテナは超短縮型にならざるを得ません。 それだけに輻射効率の良いアンテナは難しくなるのですが上手に作れば十分楽しめるだけのものができます。

写真は手持ちのアンテナ製作用パーツです。 今回は活用する最後のチャンスと考えて長いこと温存していた専用の部材を投入することにしました。 茶色のパイプ状がグラスファイバ・ロッドで、以前HF帯のモバイル運用が流行ったころヘリカル巻き短縮アンテナの製作によく使われた素材です。 その下がそれに適合するコネクタ部でM型になっています。一番下は6段のロッド・アンテナで30m Bandのホイップ・アンテナに使ったものと同じです。完全に伸ばした全長は101.5cmのものです。 各部材の入手・代替などに関する情報は後ほどあります。

☆

再びモバイル用アンテナ製作の話に戻ります。 30m Bandは楽しいHAMバンドですが30mのアンテナだけではオンジエアの幅が狭くなってしまいます。これから40m Band用のモバイル・ホイップ・アンテナを製作します。やはりHF帯のメインストリートに出たいですね。 FBなアンテナができたならドライブの楽しみも広がります。

製作するアンテナの基本構造はすでに前のBlog(←リンク)で扱った30m Band用と同じセンター・ローディング形式です。 実用的な性能が得られた実績を重視し同じ形式にしました。 もう一つの理由はセンター・ローディング形式なら設計手法が確立しているため試行回数が少なく済むからです。

ヘリカル巻きの短縮型も面白そうに思ったのですが製作経験がないので諦めました。 従って既に前のBlogをご覧でしたらアンテナ形式そのものに目新しさはないでしょう。 しかし、もしお暇ならお付き合いください。 Somithing NEWはあるはずです。

【エア・ダックス・コイルと切断治具】

40m Bnadのホイップ・アンテナでも短縮コイルにエア・ダックスを使います。 コイルはボビン(巻枠)に自分で巻いて作れるパーツですが、手持ちを温存する意味もないので積極的に使うことにします。

型番はNo.401016で30m Bnadのホイップ・アンテナに使ったものと同じです。 流石に太めの線を巻いた空芯コイルだけあってQu=300が得られます。自作すればもう少しHigh-Qなコイルも十分可能なのですがQu=300はけして悪い数字ではありません。かなり良い性能と言えます。 活用することにしました。

エア・ダックスの切断に使えそうなプラスチックス切断用の治具(写真手前)があったので使ってみました。 コイルの「巻き」をあまり無駄にせず綺麗に切断可能ですがそもそもエア・ダックスが手に入らないパーツなので・・・道具もあまり意味はないかも。w

【40m用センタ・ローディングANTの設計】

今回は計算してから製作を始めました。 ただし設計アプリを使うためにはアンテナ・エレメントの寸法が明確でないと始まりません。

具体的にはコイルより下側のベースセクションと上側のトップセクションの寸法です。長さと平均径が必要です。 また容量冠の有無と、もし使う場合はその寸法・構造も必要です。

下部・ベースセクションに使うグラスファイバ・ロッド(上記写真で茶色のパイプ)は、長さ:L=140cm、元口径=1.4cm、先端径=0.55cm、肉厚=1mm程度のものです。ただし細い先端部は使いません。 コイルより上部のトップセクションは伸縮可能なロッド・アンテナ(テレスコーピック・アンテナ)を使います。 従ってグラスファイバ・ロッドは適当な寸法で切断しました。

センタ・ローディング・アンテナの輻射効率はRF電流の腹にあたる下部セクションの影響が大です。 全長を一定とすればRF電流が小さくなるコイルより上部を長くするよりもRF電流が大きい下部セクションを長くした方が有利です。ボトムローディング形式は構造的に有利ですが輻射効率では最低と言えます。 だからと言って短絡的な考えでコイルを最頂部に置くのがベストかと言えば、そうではありませんが・・・。

(参考:簡単に言うと先端に行くほど共振に必要なインダクタンスが増えHigh-Qなコイルの製作・保持が難しくなります。接地抵抗を仮定しローディング・コイルのQをパラメータとして計算すれば最適なコイルの位置が求まります)

種々の要素を検討してグラスファイバ・ロッドは元口から82.5cmのところで切断しました。 ただし一部はコネクタ部とコイルのサポートに取られるので電気的に有効な長さは実測67cmになりました。 上部セクションはロッド・アンテナそのものなので長さ101.5cmありますが、使用時にはやや縮めて使うことを想定し96cmとして計算しています。 先端の容量冠は実際は8の字型ですが等価的に直径8cmの円形でスポークは4本として計算しました。 接地抵抗はとりあえず10Ωとしておきますので効率計算は参考値です。

必要なローディング・コイルのインダクタンスは約42μHと計算されます。エア・ダックス・コイル:No.401016はちょうど40回巻きが必要です。 コイルのバラツキおよび計算誤差などを考慮して数回(3回)多めに切断しておきます。

【ローディング・コイルの調整】

おおよそのインダクタンスは計算で求めてあります。

エアダックス・コイルのインダクタンスは付属のチャートから求められますが、かなりラフなものです。 実際にはQメータで測定してインダクタンスを確認しておきました。(どうせタップで加減するので事前の精密な測定は必要ありません)

上部エレメントからクリップ付きリード線を出しコイルの巻き線を摑んで共振する周波数を探ります。

超短縮なアンテナは狭帯域になりがちです。SWRが下がり実用となるのは共振周波数付近の狭い範囲になります。ほぼスポット周波数と言えます。正確に7050kHzあたりで共振するようコイルを調整しました。 実際に使用する際は上部のロッド・アンテナ部分を伸縮させてオンジエアする周波数にぴったり合うようシビアに加減する必要があります。 もしもブロードな周波数特性を示すならその短縮アンテナの輻射効率はかなり低い可能性があります。これはご参考までに。

コイルの調整に際してロッド・アンテナの長さは±に調整できるよう適度に縮めた状態で行ないます。 伸ばし切った状態で決めたら共振周波数を低い方へ調整できません。

【ケースを被せてローディング・コイル完成】

防水・防滴構造ではありませんが多少の天候変化なら大丈夫なようにしておきます。

コイル全体をプラスチックス製のケースに収納してあります。 このケースは200mlのサンプル容器というものです。 蓋の部分を下にして逆さまに使っています。ローディング・コイルは蓋の部分に固定されています。

容器は適当な寸法の手持ちがあったので使いましたが100均で様々なものが手に入るので適当なものを見つければ良いでしょう。なお金属製の容器はインダクタンスやQへの影響が大きいため使うべきではありません。

もし走行しながら使えるアンテナを作りたいなら十分な検討が必要です。 破損がないように構造や部材を吟味しなくてはならないでしょう。

このアンテナは車をどこかに停めて半固定でのオンジエアで使うことを前提に考えています。移動運用地に到着してからアンテナ基台に装着します。 着脱で簡単に壊れないよう相応の機械的な強度は考えていますが停車した状態で使うべきでしょう。 アンテナ基台もそれほど大型ではありませんから車体への固定が十分に強固とは思えません。ある程度可能かもしれませんが大きめのアンテナを付けたままの走行は安全ではないでしょう。

【コイルは発熱する】

コイルのQが無限大でない限り必ずロスが発生します。5Wと言ったQRPなら発熱量はたかが知れていますが移動局の限度いっぱいの50Wも出すと馬鹿にできません。

このアンテナの場合、入力電力の約35%がコイルで熱になる計算です。Qu=300というかなり良いコイルを使っていてもそれだけのロスが発生します。 例えば送信電力:50Wとしてコイルでの損失は18Wくらいになります。これは無視できない発熱量です。

テストの段階で連続的な送信を行なったところ「共振周波数の跳躍」が見られました。 約30kHzほど上昇したのです。温度上昇によって製作時の機械的なストレスが解放されたものと考えられます。 その後は50Wでのオンジエアでも変化を感じないので安定したようです。

【インピーダンス・マッチング】

C-L型のインピーダンスマッチング回路を付けました。

この部分も30m Bandのホイップ・アンテナと同様の構造です。ただし容量値は異なります。

給電点のインピーダンスを想定して計算すると、必要な容量値は約610pFになりす。計算自体がアバウトなものですから680pFのディップド・マイカ・コンデンサで間に合わせました。 マッチング回路のインダクタンスは約0.54μHでローディング・コイルに含めることで省略できます。

写真でアンテナ下部の構造がわかると思います。グラスファイバ・ロッドは同軸ケーブル(10D-2V)を剥いて作った網線で覆われています。

これは下部エレメントを低抵抗に作ってロスを減らし、しかも太くすることで静電容量を大きくする目的があります。 アンテナのキャパシティをできるだけ大きくすることで、なるべく少ないインダクタンスのローディング・コイルで共振させるようにします。

もちろん銅の網線が裸のままでは錆びてくるのでテープを巻いておきます。ビニル・テープなどではなくて自己融着テープが最適です。自己融着テープは高周波的な特性も悪くありません。自己融着テープも最近はホームセンターの電材コーナーに置いてあります。 もし手に入れば太い熱収縮チューブを使うと体裁よく仕上がります。

【マッチング部の防水】

マッチング回路のコンデンサを含めてテーピングしておきます。これでコンデンサが取れてしまうことも防げます。

この部分で意外に厄介なのはコネクタ部とのハンダ付けです。 コネクタ部分はクロームメッキされていて、普通のハンダ付けができないからです。これはコイルより上部のロッド・アンテナ部分も同じです。

ホームセンターへ行くとホワイト・メタル用と言うフラックスが見つかります。是非ともそれを使ってハンダ付けすべきです。

メッキを剥がす方法もありますが材質によっては母材にハンダ付けできないことがあります。 機械的にカシメても良いので確実な接続ができるようにします。高周波回路は接触不良を嫌いますから効率低下が起こらぬようにしたいものです。

(注意:フラックスは酸化性が強いので残存していると錆が出ます。十分な洗浄を!)

【10MHzと7MHzのWhip Antenna】

完成した7MHzのアンテナを並べてみました。左が先に作った10MHzで右が7MHzです。 基本的に同じ構造ですので良く似ています。

写真ではわかりませんが後から作った7MHzは改良された箇所がたくさんあります。 やはり2つ目の製作ともなると最初の経験が活きてきます。 部材も残り物の間に合わせから専用品に代わった部分もあって作りやすさにも違いがありました。

ローディング・コイルのサポート構造は特に進歩した部分です。 10MHz用は主要部分をエポキシ系の接着剤(アラルダイト・ラピッド)で固定し、材質的にエポキシ系で無理があった所をセメダイン・スーパーXという万能接着剤で固定していました。全面的に接着剤に頼る方法です。 7MHz用ではエアダックス・コイルの構造に着目し蓋の部分に樹脂のセパレータ(4本)に合わせた穴加工を行なって固定しました。接着剤は要所に必要最低限だけです。機械的な強度はずいぶん向上し、見た感じも良くなっています。

まったく異なるタイプのアンテナを作ったほうが自作としては面白いのですが、同じ構造なら製作経験を活かすことができ改良に繋がります。実用品を作るという趣旨から言えば悪くない選択だったのではないでしょうか。

【車載した様子】

写真は車載した様子です。コイルより下部のベースセクションが長くなったため10MHzにも増して印象的になりました。

全長は約182cmあります。 装着して走行することはないので支障はないと思います。 コネクタ部分が専用品になったのでベース部分の機械的な強度はずいぶん向上したと感じます。 長くはなっても安心感はアップしています。

写真では見えにくいですが頂部に8の字型のキャパシティ・ハット(容量冠)が付いているのも10MHzのホイップANTに同じです。

【磁石アース板】

周波数が低くなったことからボディーとの結合容量の不足が気になりました。 写真のように小型版(強磁力の方)を2枚使って調整していたのですが、A4版の大きい方を追加してみました。

多少の変化は見られますが大きな違いはないことがわかったので現在は写真の状態で実用しています。 もちろん磁石アース板なしでは不安定なうえ調整も狂ってしまいまったくダメです。(笑)

【7MHz Whip Antennaの共振特性】

写真はnanoVNAで観測した7MHzホイップ・アンテナのSWR特性です。7.0MHzを中心に±500kHzの範囲で観測しています。

写真を見ますとSWRが低くくて使用可能な周波数帯域幅はたいへん狭くなっています。 スポット的と言っても良いでしょう。 高い輻射効率を狙ってできるだけロスを減らした短縮アンテナはかなりHigh-Qになります。 そのため実質的に共振周波数付近のごく狭い周波数範囲でしかオンジエアできません。

FT-8やJT-65(廃れましたが・笑)のようにスポット周波数で運用するモードなら運用中の支障はまったくありません。 CWの場合はCWバンドの低端と高端ではかなり離れているため運用周波数に合わせてアンテナ先端の伸縮により微調整する必要があるでしょう。 同様にSSBでも実際に使う周波数に応じた微調整を行なえば良好な輻射効率でオンジエアできます。

全長は約182cmと10MHz版より30cmくらい長くなっていますが、1/4・λに対する短縮率は約83%と(=17%の長さしかない)むしろ「小さなアンテナ」になっています。そのため輻射効率も少し低下しています。これが現実的なサイズなのでやむを得ないと思います。 あとはうまく電波が飛んでくれたら良いのですが・・・

帯域幅が狭く効率も低いのは超短縮アンテナにならざるを得ないHF帯移動運用の宿命と言えます。 こんなことを書くと混乱するかもしれませんが「アンテナのQは低いほどFB」なのです。しかし損失が大きくなるような方法でLow-Qにしたのでは意味がありませんけれど・・・。おわかりでしょうか?(笑)

【テスト・オンジエアの様子:FT-8】

近くの空き地で移動運用のテスト・オンジエアです。 何かあってもシャックにすぐ戻れるごく短距離の移動です。

共振周波数の調整がやや甘かったのですが、まずまず良く飛んでくれました。

CQを出したところ数局に呼んでいただけました。 コンデイションの影響もあるとは思いますが、約83%短縮という超短縮アンテナでも十分な実用性能が得られています。見かけスマートな市販ANTよりも効率はずいぶんマシでしょう。

移動運用には様々なスタイルがあります。ポータブルなQRP機を持ってフィールドに出かけて波を出すのは楽しいものです。私もFT-817なら持ってます。 しかし弱すぎる波では交信相手はだいぶ苦労するでしょう。 私の希みは:たとえ移動運用の貧弱な設備ではあってもできるだけ良い波を出したいのです。 なるべく楽に交信して頂きたいと思っています。 ですからあえてQRPには拘らず事情が許せば法定内で可能なだけのパワーを出しアンテナ系の輻射効率も極力高くありたいのです。 アマ無線は交信できてこそ無線通信です。せっかく出かけた移動運用がボウズじゃ悲しいじゃありませんか。hi

参考:QRPpでkm/Wを競うにはPOTAではなくSOTAが向いています。V/UHFなら標高で飛距離を稼ぐことができるからです。短縮なしフルサイズのアンテナやビームアンテナも使えます。HF帯よりノイズや混信が少ないのも有利です。

【PSKRでも飛びを確認】

トランシーバの受信感度には20dB(電圧で10倍、電力で言えば100倍)以上の余裕があってかなり低効率なアンテナでもよく聞こえるのが当たり前になっています。そうでないと耳の悪いトランシーバと言われてしまいます。w

しかし送信で20dBの余裕は容易ではありません。アンテナのロスを見込んで100倍のパワーに・・・など非現実的です。アンテナの数%の効率の違いに拘るのはそのためです。その数%が飛びには大いに影響します。

そのアンテナを繋いでみたらよく聞こえるからと言って、それはまったくの気休めに過ぎないかも知れません。本当のことは送信した時にわかります。

飛び具合の確認のために7041kHzでオンジエア・テストしてみました。 7041kHz/FT-8は基本的にJA局のみがオンジエアしています。 これはバンド使用区分からやむなくそうなったものと承知しています。

従って受信レポートは海外局からは得られません。 たまたま韓国に1局だけ7041kHzをワッチしていた局がいたようです。 他の日のテストでも国内各局にまんべんなく飛んでくれたのでこのアンテナはかなり旨くいったと言えるでしょう。 もちろん短縮なし・フルサイズの固定局のアンテナと比べちゃいけませんけどね。(笑)

こんどは夜間のDXタイムを選んで7074kHz/FT-8でテストしたいと思います。果たしてどれくらい飛んでくれるでしょうか。(現在は7074kHzで国内局を呼ぶことも可となりましたが、JAどうしの交信は7041kHzがメジャーなようです。DXerには有難いことです)

☆

似たようなアンテナを作るだけですから作るつもりのない人には面白味に欠けたBlogだったでしょう。 寸法図など諸元は省略しましたが、もし参考資料としてご入用でしたら連絡いただけたらと思います。 逆に本当に作ってみたいお方にとってはまだまだ情報不足を感じるはずです。

わからない部分は具体的にお尋ねになってください。私のわかる範囲で返信差し上げます。 製作工程を一からすべて教えろとか、費用を出すから代わりに同じものを作ってくれ等のご要望には応じかねます。 製作例は参考に過ぎないので、あとはみずからも考え、工夫し、手を動かし、完成させてください。 きっと旨く行きます。(笑)

調べてみて驚いたのですが、このアンテナ製作で使ったグラスファイバ・ロッドとそれ専用のM型コネクタ部は現在でも入手可能でした。製作に使ったものは25年以上も前に手に入れたものだったからです。

先端部のロッド・アンテナは昔HAMフェアで購入したもので同じものの入手は難しいかも知れません。 6段式で伸ばした全長は101.5cm(ネジ部含む)、収縮時の長さは20.3cmです。元部分の太さは7mmあります。 長さは少々違っても支障ありません。コイルのタップ位置をわずかに動かせば共振できます。 上記の寸法にこだわることなくネット通販など手に入り易いものを使いましょう。3段式で50cm程度の物でも十分です。

エア・ダックス・コイルの代用は幾らでも可能です。 塩ビやアクリル樹脂のパイプに巻いて所定のインダクタンスが得られるように作ればOKです。 理想を言えば内径85mmのボビンにφ1.6mmの巻線を巻き幅60mm(ピッチ約2.9mm)で22回巻くとHigh-Qなコイルが作れます。さらに2〜3回余分に巻いて調整の余裕を持たせます。 密着巻きではなく必ずスペース巻きで作ります。 密着巻きでは巻線相互の「近接効果」のためQが上がりません。(重要なノウハウ・笑)

写真は「さきたま古墳公園」(埼玉県行田市:POTA JP-1178/JCC-1306)でオンジエアした際のものです。 自作した7MHzホイップ・アンテナは各地のPOTA運用(←リンク)で存分に活躍してくれています。 たくさんのQSOありがとうございます! ではまたどこかの公園から。 de JA9TTT/1

(つづく)fm

2024年3月10日日曜日

【HAM】Parks on the Air : POTA

【パークス・オンジエア:公園からオンジエア】

abstract

Have you heard of POTA? POTA stands for "Parks on the Air" and is an on-air activity of HAM stations from the parks. It is a US-derived activity derived from Summit on the Air (SOTA). POTA has already become a worldwide activity. You can easily get started. The first step is for you to become a 'Hunter'. Then, once you have registered an account on the POTA website, all you have to do is call a POTA station. No hassle. It's even more fun when you become an 'Activator'. Go out to the park and open a mobile radio station. But there is nothing difficult about it. All you have to do is go to the park and enjoy the HAM Radio. (2024.03.10 de JA9TTT/1 Takahiro Kato)

【POTAって?】

最近オンエアしていると"CQ POTA DE JA9・・・"という呼びかけを聞くことが多くなっていました。 コンテスト局のようではないし誰とでも交信しているようです。 たまにはこちらが呼ばれることもあって「ポタって何だろう?」と思っていました。

POTAというのは"Parks on the Air"・・・すなわち『公園でオンジエア』という意味のようです。 そう言えば以前"SOTA"って言うのを聞いたことがありました。 Rigとアンテナを担いで登山して山頂(Summit)からオンジエアし、アワードをねらうと言ったHAMの活動だったはずです。 その公園版がPOTAらしいのです。

軟弱な当局では重たいリグやバッテリ、さらにアンテナに加えテントと言った登山装備一式を担いで山に登るなんてムリムリだと思っています。(笑) しかし公園なら平地にもありますし、徒歩という「縛り」もないので自動車のまま行ける所もあるでしょう。 デキル可能性があります。

☆

これは私的感想に過ぎませんが:HAMのアクティビティも漫然と交信しているだけではいずれ低下してきて当然かも知れません。 QSLカードやアワード集めは楽しいものですが、ある日ふと「単なる紙集めじゃないか!」って気付いて疑問に感じてしまったなら・・・せっかくの趣味も楽しさが希薄になってしまいそうです。 ローカルさんとのおしゃべりにもマンネリズムを感じてきたら・・・趣味を長く楽しむために何か活性化できることはないでしょうか? その一つがPOTA活なのかも知れません。もちろん、各局さんそれぞれのお考えもあるでしょう。

画面はさっそくPOTAのサイト(←リンク)へ行ってアカウント登録した様子です。

◎ POTA活には2つがある。

一番簡単なのはHunter(ハンター)で、これは公園からオンジエアする移動局を呼ぶだけです。あとは何もしなくてOKです。(カード交換さえも必要ありません)

もちろん電子発行されるアワード(このBlogの最後を参照)を希望するのでしたらアカウント登録だけは必要です。しかしそれ以外はいっさい何も要りません。だからとっても簡単です。 アカウントの登録は気が向いてからでも大丈夫です。過去の交信もちゃんと反映されますので。 あとはPOTA局を見つけたら交信しましょう。休日の午後たくさん出ています。

もう一つは公園からオンジエアするActivator(アクティベータ)です。こちらはRigを持って公園から決められたルールに従ってオンジエアします。 まあこれも特に難しいことはなくて肝心なのは無理せず楽しくオンジエアすることです。 そして移動運用が終わったら一つだけ必須の作業があります。POTAのサイトへADIF形式でLogを提出することです。このLogのおかげでハンターは何もしなくて良い訳なので・・・。 完全な交信が10局以上できるとその公園がアクティベーション(活性化)できたことになります。

もしも興味が湧いてきたらPOTAのサイトや関連のサイトなどを参照されてください。YoutubeでPOTAの動画も見つかります。 以下、POTAに興味を持つ切っ掛けになったら幸いです。 もちろん何の興味も感じないのでしたら早々のお帰りがベストです。

【POTAできる公園は?】

わたしはハンターよりもアクティベータの方に興味を持ちました。 公園から移動運用してみたいと思ったのです。

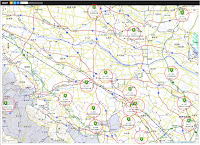

しかしどこかその辺の公園に行ってオンジエアすれば良いわけではないようなのです。 あらかじめ登録され番号がついている公園からオンジエアしないと有効な交信になりません。 ではどんな公園があるのでしょうか? 調べるサイト(←リンク)があって日本全国の公園を地図上でビジュアルに調べることができます。

画面は付近の公園を調べた結果です。あまり小さな公園は対象ではないようです。また大きな公園でも市町村が管理する公園は登録されていません。 おもに国立や県立の大きめの公園が登録されています。

【参考:公園番号の変更】

従来:JA-1234のように番号がついてましたが2024年3月初めよりJP-1234のように変更されました。JA→JPになっただけで数字部分は変わっていないようです。

残念ながら5分で行けるような公園はありませんでした。 しかし容易に出掛けられそうな公園がたくさん登録されています。 知らなかったような公園もあってオンジエア目的でなくても興味が湧くところもありました。 これらの中から先ずは行き易そうな公園を選んでテスト・オンジエアしましょう。

【雉岡城址からPOTA】

近所の公園に「上武県立自然公園」がありました。この公園は非常に広大なものです。

全国各地に指定されている自然公園の一つで昭和25年に指定されたそうです。国の自然公園制度によって誕生したそうです。(知りませんでした・笑)

埼玉県北西部の広域をカバーする公園です。POTAのルールによればその公園の中ならどこからのオンジエアでも有効です。

さっそく調べたら「雉岡城址」という市内の公園が含まれていました。元々ここは児玉郡児玉町でしたが平成の合併で本庄市になった所です。25分もあれば行けるはずです。

Googleストリートで確認したら駐車してオンジエアできるスペースもありました。 先ずはここから波を出してみましょう!

オンジエアの最低限のルールは、アンテナ、無線機、オペレータのすべてが公園内にあることです。 あとはそれぞれの公園のルールに従う必要があります。 車載だけで完結できれば車外にアンテナを建てる必要もないのでまずトラブルにはなりません。 あとは所定の駐車スペースに停めて楽しくオンジエア開始です。

【移動運用の準備】

普段は無線機を車載していません。必要なつど積み込むようにしています。 移動運用で必要になる道具は結構色々あります。 無線機やアンテナだけでなく電源やパソコンが必需品です。もちろんオペレータ・ライセンスや無線局免許状も。

音声やCW(無線電信)でオンエアなら無線機とアンテナ、あとはメモ帳でもあればPOTAできます。 おもにV/UHF帯のFMやSSBでオンジエアされるPOTA局もあって手軽にお楽しみのようです。 カートランシーバと車載ホイップなら常設しておけますからね。

楽しみ方は人それぞれです。 わたしはちょっと遠方の局とも交信したいと思っています。それでHF帯(短波帯)でオンジエアしたいのです。 このまえ作った10MHzの短縮ホイップ・アンテナを使い無線機もHF帯に出られるIC-7300を使うことにしました。 ほかにも遠くとできそうな見晴らしの良い高台から6m Bandと言うのも面白そう。しかもEスポでも出たら九州や北海道も・・・。Eスポは6月ころ初夏が狙い目です。

運用モード(電波形式)はデジタルモードをメインに考えています。このモードは弱い電波でも交信し易いからです。ノイズにもかなり強いです。 さらに自動でLogに記入できるなど利便性もよく短い時間での移動運用には最適だからです。 ただ、HF帯のPOTAハンターにはCW局もかなり多いのでCWでもオンジエアすべきなのかも知れません。 良い条件の公園が見つかったら改めてCWやSSBでじっくりオンジエアしたいですね。電鍵やマイクを持って出掛けましょう。

【移動局を開局】

始めたばかりなので車載のセッティングや運用方法は試行中の段階です。

デジタルモード(FT-8など)の場合いくつか注意が必要だと思っています。 パソコンを使うことになりますが使うパソコンは時刻同期が必要です。

その方法としてGPSを使う方法があります。 またネット接続が可能ならタイムサーバーを使って同期する方法もあります。

どちらも可能な機材は持ってますがeQSLの即時発行を狙ってネット接続を試しました。iPhoneのディザ機能を使います。よほど田舎でなければ携帯回線が使えます。近隣の公園なら大丈夫そうです。

実験を兼ねた初運用はうまく行ってパソコンの時刻同期もeQSL発行もできました。 ただしeQSLの発行は別途行なう方が良いと言う結論です。

一つにディザは意外に不安定なことがあります。eQSLの発行モレや重複などの問題もあるので交信即発行でない方が安心です。 従って必ずしもインターネット環境は必要なく、パソコンの時刻同期はGPSを使う方法でも良いでしょう。 もちろんオンジエアのアナウンスをPOTAサイト等に流すにはネット環境があった方がFBです。

運用のあと本当に必要なのはPOTAサイトにLogを提出することです。 JCC/JCGのサービスにもなるのでeQSLは発行すべきでしょう。しかしPOTAサイトへのLog提出が優先です。POTAのLogデータを作るときeQSLのデータも簡単に作れるのでQSLカードの発行はその時にやれば良いと言う結論です。 この辺りは各局の好みにあったやり方をすれば良いはずです。

【上武県立自然公園のアクティベーション】

13局と交信できアクティベーション成功です。

10MHzはニッチなバンドなのでオンジエアする国内局が少ないのが心配でしたが、あんがい簡単に規定の交信数に達しました。 複数コールサインをお持ちのお方に何回も呼んでいただいたフシもあるのですが・・・(笑)

Turbo HAM Logの交信データをPOTAサイト用のADIF形式に変換して頂けるJL1NIE:友部さんのサイト(←リンク)があります。 ADIF形式への変換は面倒に感じますがCSV形式で出力したTurbo HAM Logの交信データを用意するだけで良いため難しくはありません。具体的な作成手順はリンク先サイトに詳しいです。私も利用させて頂いております。VY-TNX!

上武県立自然公園:JP-1150(JA-1150)の運用データは既にアップロード&承認済みです。貴局のPOTA活成果として反映されていると思います。 お呼びいただき有難うございました。

☆ ☆

【群馬の森:JP-1322(JA-1322)でPOTA】

「群馬の森」は群馬県高崎市にある公園です。 以前行ったことがあってPOTAの運用が可能そうでした。

きちんと管理された公園の場合、運用する時間帯が問題になります。冬季ですとあんがい早い時刻で閉園になるところが多いようです。 運用バンドによっては夜間に掛かる時間帯が有利な場合もあるのですが、公園から出られなくなったら困ります。

・・・と言うことでベストとは言えない時間帯のオンジエアになりました。 それでも沢山のお方と交信できました。 JP-1322(JA-1322)の運用データもアップロード&承認済みです。 PSKRのレポートを見たら海外のハンターにもサービス可能そうなのですが、それにはやはり時間帯を選ぶ必要がありそうです。

【JP-1322(JA-1322)からの飛び方】

日本国内のほか、アジア・オセアニアならまずまず飛びそうな感触です。 粘り強く呼んでみると言った努力が必要かもしれません。

自宅で運用しているWSPRのレポートも総合すると、例えば30m Bandは日没から1時間〜2時間くらいがDXに良く開けるようです。HF帯はそれぞれバンドの性格に合わせた運用時間帯の選び方が肝心です。

移動運用の限定された設備ですから、固定局と同じようには行かないと思いますがこうした時間帯をねらってCQ POTAを出すのも面白そうです。 JAのPOTA局を狙うDX局もいるそうですからいずれやってみましょう。

今のところ短時間のオンジエアばかりなのでゆとりがありません。 ぼちぼち春ですが、もっと暖かくなってきたら時間を気にせずにジックリやろうと思っています。 どうぞお相手をよろしく。

【さっそくアワードが!】

これはPOTAを始めたら誰でもまず始めにもらえそうなアワードです。 ハンターがPOTA局と10交信するともらえます。

条件を満たしたらしく何の申請もせずに自動的に発行されました。 PDFの電子データなので「紙」のアワード派にはちょっと残念かもしれません。 紙派のお方は良質な台紙を用意して高品位印刷すればシャックに飾れるアワードになりますね。

POTAには他にも様々なアワードがあって、例えば「早番」「遅番」と言った面白いものもあります。 まだまだいっぱい有りますが急がず慌てずにゆっくり楽しみましょう。アワードもらえたなら活動の足跡にもなります。まあ競ってまで集めたいとは思いませんが。hi

詳しくはPOTAのサイトで「Awards」をご覧になってください。

高齢者の域にある当局には電子データのアワードは有難いくらいです。 何だか意味のわからない「紙」がいっぱい残ってもいずれ家族の迷惑になってしまうでしょう。 アワードを頂くのは嬉しいものですが電子データもFBですね。(笑)

☆

車載アンテナはPOTAを目的に開発した訳ではありません。 しばらくぶりに移動運用してみたいと言うHAMの活性化が目的でした。 ローカルのJCC/JCGにはHF帯のアクティブティが高くないところもあります。移動運用でサービスできたら・・という思惑もありました。 あと、車載のAC100V電源で無線をやってみたいと言うのも動機の一つでした。

ちょうどその時POTAと言う活動を目にしました。 SOTA(Summit on the Air)は体力的に難しくてもPOTAならできそうだと言うことで興味を持ったのです。 移動地によってはJCC/JCGサービスも兼ねるので皆さんとお会いできるチャンスが増えたらFBです。 どうやら私のPOTA活はHAM活性化にもピッタリみたいです。 かぼそい波かも知れませんがJA9TTTの"CQ POTA"が聞こえたらぜひ呼んでやって下さい。 ではまた。 de JA9TTT/1

(おわり)nm

abstract

Have you heard of POTA? POTA stands for "Parks on the Air" and is an on-air activity of HAM stations from the parks. It is a US-derived activity derived from Summit on the Air (SOTA). POTA has already become a worldwide activity. You can easily get started. The first step is for you to become a 'Hunter'. Then, once you have registered an account on the POTA website, all you have to do is call a POTA station. No hassle. It's even more fun when you become an 'Activator'. Go out to the park and open a mobile radio station. But there is nothing difficult about it. All you have to do is go to the park and enjoy the HAM Radio. (2024.03.10 de JA9TTT/1 Takahiro Kato)

【POTAって?】

最近オンエアしていると"CQ POTA DE JA9・・・"という呼びかけを聞くことが多くなっていました。 コンテスト局のようではないし誰とでも交信しているようです。 たまにはこちらが呼ばれることもあって「ポタって何だろう?」と思っていました。

POTAというのは"Parks on the Air"・・・すなわち『公園でオンジエア』という意味のようです。 そう言えば以前"SOTA"って言うのを聞いたことがありました。 Rigとアンテナを担いで登山して山頂(Summit)からオンジエアし、アワードをねらうと言ったHAMの活動だったはずです。 その公園版がPOTAらしいのです。

軟弱な当局では重たいリグやバッテリ、さらにアンテナに加えテントと言った登山装備一式を担いで山に登るなんてムリムリだと思っています。(笑) しかし公園なら平地にもありますし、徒歩という「縛り」もないので自動車のまま行ける所もあるでしょう。 デキル可能性があります。

☆

これは私的感想に過ぎませんが:HAMのアクティビティも漫然と交信しているだけではいずれ低下してきて当然かも知れません。 QSLカードやアワード集めは楽しいものですが、ある日ふと「単なる紙集めじゃないか!」って気付いて疑問に感じてしまったなら・・・せっかくの趣味も楽しさが希薄になってしまいそうです。 ローカルさんとのおしゃべりにもマンネリズムを感じてきたら・・・趣味を長く楽しむために何か活性化できることはないでしょうか? その一つがPOTA活なのかも知れません。もちろん、各局さんそれぞれのお考えもあるでしょう。

画面はさっそくPOTAのサイト(←リンク)へ行ってアカウント登録した様子です。

◎ POTA活には2つがある。

一番簡単なのはHunter(ハンター)で、これは公園からオンジエアする移動局を呼ぶだけです。あとは何もしなくてOKです。(カード交換さえも必要ありません)

もちろん電子発行されるアワード(このBlogの最後を参照)を希望するのでしたらアカウント登録だけは必要です。しかしそれ以外はいっさい何も要りません。だからとっても簡単です。 アカウントの登録は気が向いてからでも大丈夫です。過去の交信もちゃんと反映されますので。 あとはPOTA局を見つけたら交信しましょう。休日の午後たくさん出ています。

もう一つは公園からオンジエアするActivator(アクティベータ)です。こちらはRigを持って公園から決められたルールに従ってオンジエアします。 まあこれも特に難しいことはなくて肝心なのは無理せず楽しくオンジエアすることです。 そして移動運用が終わったら一つだけ必須の作業があります。POTAのサイトへADIF形式でLogを提出することです。このLogのおかげでハンターは何もしなくて良い訳なので・・・。 完全な交信が10局以上できるとその公園がアクティベーション(活性化)できたことになります。

もしも興味が湧いてきたらPOTAのサイトや関連のサイトなどを参照されてください。YoutubeでPOTAの動画も見つかります。 以下、POTAに興味を持つ切っ掛けになったら幸いです。 もちろん何の興味も感じないのでしたら早々のお帰りがベストです。

【POTAできる公園は?】

わたしはハンターよりもアクティベータの方に興味を持ちました。 公園から移動運用してみたいと思ったのです。

しかしどこかその辺の公園に行ってオンジエアすれば良いわけではないようなのです。 あらかじめ登録され番号がついている公園からオンジエアしないと有効な交信になりません。 ではどんな公園があるのでしょうか? 調べるサイト(←リンク)があって日本全国の公園を地図上でビジュアルに調べることができます。

画面は付近の公園を調べた結果です。あまり小さな公園は対象ではないようです。また大きな公園でも市町村が管理する公園は登録されていません。 おもに国立や県立の大きめの公園が登録されています。

【参考:公園番号の変更】

従来:JA-1234のように番号がついてましたが2024年3月初めよりJP-1234のように変更されました。JA→JPになっただけで数字部分は変わっていないようです。

残念ながら5分で行けるような公園はありませんでした。 しかし容易に出掛けられそうな公園がたくさん登録されています。 知らなかったような公園もあってオンジエア目的でなくても興味が湧くところもありました。 これらの中から先ずは行き易そうな公園を選んでテスト・オンジエアしましょう。

【雉岡城址からPOTA】

近所の公園に「上武県立自然公園」がありました。この公園は非常に広大なものです。

全国各地に指定されている自然公園の一つで昭和25年に指定されたそうです。国の自然公園制度によって誕生したそうです。(知りませんでした・笑)

埼玉県北西部の広域をカバーする公園です。POTAのルールによればその公園の中ならどこからのオンジエアでも有効です。

さっそく調べたら「雉岡城址」という市内の公園が含まれていました。元々ここは児玉郡児玉町でしたが平成の合併で本庄市になった所です。25分もあれば行けるはずです。

Googleストリートで確認したら駐車してオンジエアできるスペースもありました。 先ずはここから波を出してみましょう!

オンジエアの最低限のルールは、アンテナ、無線機、オペレータのすべてが公園内にあることです。 あとはそれぞれの公園のルールに従う必要があります。 車載だけで完結できれば車外にアンテナを建てる必要もないのでまずトラブルにはなりません。 あとは所定の駐車スペースに停めて楽しくオンジエア開始です。

【移動運用の準備】

普段は無線機を車載していません。必要なつど積み込むようにしています。 移動運用で必要になる道具は結構色々あります。 無線機やアンテナだけでなく電源やパソコンが必需品です。もちろんオペレータ・ライセンスや無線局免許状も。

音声やCW(無線電信)でオンエアなら無線機とアンテナ、あとはメモ帳でもあればPOTAできます。 おもにV/UHF帯のFMやSSBでオンジエアされるPOTA局もあって手軽にお楽しみのようです。 カートランシーバと車載ホイップなら常設しておけますからね。

楽しみ方は人それぞれです。 わたしはちょっと遠方の局とも交信したいと思っています。それでHF帯(短波帯)でオンジエアしたいのです。 このまえ作った10MHzの短縮ホイップ・アンテナを使い無線機もHF帯に出られるIC-7300を使うことにしました。 ほかにも遠くとできそうな見晴らしの良い高台から6m Bandと言うのも面白そう。しかもEスポでも出たら九州や北海道も・・・。Eスポは6月ころ初夏が狙い目です。

運用モード(電波形式)はデジタルモードをメインに考えています。このモードは弱い電波でも交信し易いからです。ノイズにもかなり強いです。 さらに自動でLogに記入できるなど利便性もよく短い時間での移動運用には最適だからです。 ただ、HF帯のPOTAハンターにはCW局もかなり多いのでCWでもオンジエアすべきなのかも知れません。 良い条件の公園が見つかったら改めてCWやSSBでじっくりオンジエアしたいですね。電鍵やマイクを持って出掛けましょう。

【移動局を開局】

始めたばかりなので車載のセッティングや運用方法は試行中の段階です。

デジタルモード(FT-8など)の場合いくつか注意が必要だと思っています。 パソコンを使うことになりますが使うパソコンは時刻同期が必要です。

その方法としてGPSを使う方法があります。 またネット接続が可能ならタイムサーバーを使って同期する方法もあります。

どちらも可能な機材は持ってますがeQSLの即時発行を狙ってネット接続を試しました。iPhoneのディザ機能を使います。よほど田舎でなければ携帯回線が使えます。近隣の公園なら大丈夫そうです。

実験を兼ねた初運用はうまく行ってパソコンの時刻同期もeQSL発行もできました。 ただしeQSLの発行は別途行なう方が良いと言う結論です。

一つにディザは意外に不安定なことがあります。eQSLの発行モレや重複などの問題もあるので交信即発行でない方が安心です。 従って必ずしもインターネット環境は必要なく、パソコンの時刻同期はGPSを使う方法でも良いでしょう。 もちろんオンジエアのアナウンスをPOTAサイト等に流すにはネット環境があった方がFBです。

運用のあと本当に必要なのはPOTAサイトにLogを提出することです。 JCC/JCGのサービスにもなるのでeQSLは発行すべきでしょう。しかしPOTAサイトへのLog提出が優先です。POTAのLogデータを作るときeQSLのデータも簡単に作れるのでQSLカードの発行はその時にやれば良いと言う結論です。 この辺りは各局の好みにあったやり方をすれば良いはずです。

【上武県立自然公園のアクティベーション】

13局と交信できアクティベーション成功です。

10MHzはニッチなバンドなのでオンジエアする国内局が少ないのが心配でしたが、あんがい簡単に規定の交信数に達しました。 複数コールサインをお持ちのお方に何回も呼んでいただいたフシもあるのですが・・・(笑)

Turbo HAM Logの交信データをPOTAサイト用のADIF形式に変換して頂けるJL1NIE:友部さんのサイト(←リンク)があります。 ADIF形式への変換は面倒に感じますがCSV形式で出力したTurbo HAM Logの交信データを用意するだけで良いため難しくはありません。具体的な作成手順はリンク先サイトに詳しいです。私も利用させて頂いております。VY-TNX!

上武県立自然公園:JP-1150(JA-1150)の運用データは既にアップロード&承認済みです。貴局のPOTA活成果として反映されていると思います。 お呼びいただき有難うございました。

☆ ☆

【群馬の森:JP-1322(JA-1322)でPOTA】

「群馬の森」は群馬県高崎市にある公園です。 以前行ったことがあってPOTAの運用が可能そうでした。

きちんと管理された公園の場合、運用する時間帯が問題になります。冬季ですとあんがい早い時刻で閉園になるところが多いようです。 運用バンドによっては夜間に掛かる時間帯が有利な場合もあるのですが、公園から出られなくなったら困ります。

・・・と言うことでベストとは言えない時間帯のオンジエアになりました。 それでも沢山のお方と交信できました。 JP-1322(JA-1322)の運用データもアップロード&承認済みです。 PSKRのレポートを見たら海外のハンターにもサービス可能そうなのですが、それにはやはり時間帯を選ぶ必要がありそうです。

【JP-1322(JA-1322)からの飛び方】

日本国内のほか、アジア・オセアニアならまずまず飛びそうな感触です。 粘り強く呼んでみると言った努力が必要かもしれません。

自宅で運用しているWSPRのレポートも総合すると、例えば30m Bandは日没から1時間〜2時間くらいがDXに良く開けるようです。HF帯はそれぞれバンドの性格に合わせた運用時間帯の選び方が肝心です。

移動運用の限定された設備ですから、固定局と同じようには行かないと思いますがこうした時間帯をねらってCQ POTAを出すのも面白そうです。 JAのPOTA局を狙うDX局もいるそうですからいずれやってみましょう。

今のところ短時間のオンジエアばかりなのでゆとりがありません。 ぼちぼち春ですが、もっと暖かくなってきたら時間を気にせずにジックリやろうと思っています。 どうぞお相手をよろしく。

【さっそくアワードが!】

これはPOTAを始めたら誰でもまず始めにもらえそうなアワードです。 ハンターがPOTA局と10交信するともらえます。

条件を満たしたらしく何の申請もせずに自動的に発行されました。 PDFの電子データなので「紙」のアワード派にはちょっと残念かもしれません。 紙派のお方は良質な台紙を用意して高品位印刷すればシャックに飾れるアワードになりますね。

POTAには他にも様々なアワードがあって、例えば「早番」「遅番」と言った面白いものもあります。 まだまだいっぱい有りますが急がず慌てずにゆっくり楽しみましょう。アワードもらえたなら活動の足跡にもなります。まあ競ってまで集めたいとは思いませんが。hi

詳しくはPOTAのサイトで「Awards」をご覧になってください。

高齢者の域にある当局には電子データのアワードは有難いくらいです。 何だか意味のわからない「紙」がいっぱい残ってもいずれ家族の迷惑になってしまうでしょう。 アワードを頂くのは嬉しいものですが電子データもFBですね。(笑)

☆

車載アンテナはPOTAを目的に開発した訳ではありません。 しばらくぶりに移動運用してみたいと言うHAMの活性化が目的でした。 ローカルのJCC/JCGにはHF帯のアクティブティが高くないところもあります。移動運用でサービスできたら・・という思惑もありました。 あと、車載のAC100V電源で無線をやってみたいと言うのも動機の一つでした。

ちょうどその時POTAと言う活動を目にしました。 SOTA(Summit on the Air)は体力的に難しくてもPOTAならできそうだと言うことで興味を持ったのです。 移動地によってはJCC/JCGサービスも兼ねるので皆さんとお会いできるチャンスが増えたらFBです。 どうやら私のPOTA活はHAM活性化にもピッタリみたいです。 かぼそい波かも知れませんがJA9TTTの"CQ POTA"が聞こえたらぜひ呼んでやって下さい。 ではまた。 de JA9TTT/1

(おわり)nm

2024年2月24日土曜日

【Antenna】Making a 30m-Band Whip Antenna

【30mバンドのホイップ・アンテナを作る】

abstract

The 30m band is a new HAM band in Japan; it has been authorised since 1 April 1982. Only HAMs with an advanced licence can on-air in the 30 m band. Therefore, few HAM stations on the air are available, so existing antennas are limited. High performance 30m band antennas for mobile use are unlikely. If not, it is best to build your own. I build high efficiency 30m band antennas. (2024.02.24 de JA9TTT/1 Takahiro Kato)

【30m Bandとは】

30mバンドは10.100MHz〜10.150MHzの50kHz幅を持ったHAMバンドです。WARCバンドの一つで日本では1982年4月1日から割り当てられた比較的新しいHAMバンドです。かつてはSSBもオンエアできたのですが現在は狭帯域の電波モードしか許可されていません。 具体的にはCW(無線電信)やF1D(FT-8やJT-65などのデジタルモード)が代表的です。

7MHz(40m Band)と14MHz(20m Band)の中間にあって海外へもよく飛ぶ周波数ですが2アマ以上の資格が必要なHAMバンドです。 そのためニッチなHAMバンドの扱いであり市販のアンテナは限られているようです。 他のバンドとの抱き合わせ製品はあっても10MHz用のホイップアンテナのようなバンド専用品はほとんど選択肢がありません。

ニーズがない以上、既製品が少ないのはやむを得ないとして欲しくなるようなメーカー製品がないなら自分で作るしかありません。 どんなアンテナが欲しいかと言えば輻射効率に優れるアンテナです。 モバイル局は50Wに制限されています。そんなモバイル局ではあっても、できるだけ良い(強力な)電波が飛ばせるようなアンテナが欲しいものです。 いくらスマートで体裁が良くても飛ばないものはアンテナにあらず、ダミーロードなんてねえ・・・。(考え方は各局それぞれです・笑)

☆

よく飛ぶアンテナは誰しも欲しいでしょう。しかし車載アンテナは走行中の安全を考えて機械的な強度や構造を考えねばなりません。従って自ずから寸法・形状や構造に制限が生じます。それにいくら良く飛ぶとは言っても見た目が大げさで手軽さがなければ商品性はありません。メーカー品は「売れてなんぼ」のものなのでお客さんの購買意欲を誘うような方向へ向かいます。

CWやデジタルモードを走行しながら運用することはありません。危険なので試みない方が賢明です。 半固定での運用に限定すれば輻射効率を追求する方向のアンテナが作れるかも知れません。 材料や手加工の限界で理想通りは難しいとしても可能な範囲で良いアンテナを目指したいと思います。 望むものが無ければ「自分で作る」ということです。

【なせ30m Band(10MHz)なのか?】

HF帯のメジャーバンドは7MHz帯や14MHz帯です。それに対して10MHz帯はマイナー・バンドなので空いています。従って弱い局でも拾ってもらいやすいです。これが「なぜ」の答えです。 実際に各局運用の様子を見ると昼間は国内が、また早朝や夕刻にはDX局もよく入ってきます。 国内、海外と満遍なく楽しむには向いたバンドと考えてモバイルからHF帯オンジエア最初のバンドに選びました。

【ローディング・コイルが命】

ジャンク箱の奥深くからエアー・ダックス・コイルを発掘しました。 然るべきボビンに銅線を巻いて「良いコイル」を自作しようと思っているのです。 そのためにはどんな仕様の(インダクタンスの)コイルが必要か知る必要があります。

まずは既製品のコイルで様子を見ることにしました。 そのためにエアー・ダックス・コイルを使って実測によって必要なインダクタンスを求めたいと思います。

☆

初めはそう思っていたのですが、エアー・ダックス・コイルを評価したところ思っていたよりもQが高く高性能だとわかりました。 最終的にはそのままローディング・コイルとして使うことにしました。 ただし機械的な強度に乏し構造なので実装方法に工夫を要します。

このコイルはNo.401016という型番です。 直径が40mmで、太さ(線径)が1.0mmの錫メッキ線を巻線のピッチが1.6mm(=線と線の隙間が0.6mmのスペース巻き)になるように巻けば同等品が作れます。

30m Bandの短縮型ホイップアンテナを全長が約150cmのセンター・ローディング形式で作る場合、ローディング・コイルのインダクタンスは20μH前後になります。もちろん輻射エレメントの寸法・構造によって幾分かは違ってきますが、大幅に違うことはなくてほぼ近似のインダクタンス値になるはずです。

エアー・ダックスがなければ同等のインダクタンスが得られるコイルを巻けば良い訳です。 短縮アンテナはコイルが命ですから可能な限りHigh-Qが得られるよう巻きます。 上手に巻くとこのエアー・ダックスよりずっと良いコイルが作れます。

【インダクタンスを求める】

後ほどの話で出てきますが必要なコイルのインダクタンスは計算することもできます。輻射エレメントの形状寸法などが決まればかなり精度よく求まります。

初めに計算すれば良かったのですが、いきなり実測でインダクタンスを求めてしまいました。そのような方法でも良いわけです。写真がその様子です。 実験ですのでコイルは裸の状態です。サポートも単にハンダで止めただけなので機械的な強度はまったくありません。

まずはじめにコイルより下部と上部の輻射エレメントを製作します。 上下ともに最終形状に仕上げるのがポイントです。 上下のアンテナ・エレメントができたら中間にエアー・ダックス・コイルを仮止めして調整開始です。できるだけ最終に近い状態になるようコイルを取り付けておくと仕上げの調整が容易になります。

共振が確認でき、巻き数が確定できたらコイルのサポート構造を考えることになります。 最初の写真のようにコイル全体をプラ製の容器に収める方法を採用しました。

コイルは容器のふた部分に接着剤を使って固定しました。 アンテナを付けたまま高速走行できるほどの強度は見込めませんが着脱の繰り返しや少々の風圧くらいで壊れることはないでしょう。 走行しながら使うことは想定していませんが車載アンテナは「しなる」ことを考慮して接合部分に柔軟性を持たせる構造にします。

【タップを変え共振追求】

タップの位置を変えながら共振周波数が目的の10.125MHzあたりに来るように追い込みます。

コイルはタップが取り出しやすいように一回おきに凹ませておきます。 順次タップをクリップで掴みながら共振周波数を測定します。(nanoVNAを使いました)

これでコイル何回分が必要なのか実地でわかります。 No.401016の場合、29回巻きで良いようでした。(注:これは他の要素によって幾らか違ってきます) 今回、コイルはそのまま使ってしまうのでインダクタンス値は知らなくても問題ありません。しかし知っておけば後々役立つので実測しておきました。19.57μHありました。Qu=255でした。後ほど出てきますが、計算で求めたインダクタンス:20.23μHと実測値との誤差は-3%とわずかです。

オンジエアする前の微調整は上部エレメントの伸縮によって行ないます。 上部のエレメントは6段のロッド・アンテナ(テレスコーピック・アンテナ)を使っています。 コイルを調整して共振点を求める際は完全に伸ばさずに上部エレメント1段の半分相当分だけ縮めておきます。 あらかじめ伸縮両方向の「調整しろ」を確保しておきます。もちろん全部伸ばしておきバンドの低端に合わせると言った方法もアリです。

【インピーダンス・マッチング】

短縮型アンテナの給電点インピーダンスは50Ωにはなりません。効率の良い短縮アンテナなら必ず低くなるはずです。 このアンテナの場合、おおよそ17Ωくらいが見込まれます。

インピーダンス・マッチングにはいくつかの方法があります。

(1)マッチングトランスを使う方法:透磁率の大きなフェライトコアを使いオート・トランス形式のマッチングトランスを作ります。広帯域な特性が得られるため、オート・アンテナチューナがRigに内臓される以前はよく使われました。

(2)インピーダンスマッチング回路を設ける方法:アンテナチューナと同じ考えですが、コンデンサ:Cとインダクタ:Lを使ったタイプはインダクタをローディングコイルの一部に含める方法で簡略化できます。単に給電点にコンデンサを付けるだけで済みます。(写真の方法)

(3)何もつけない方法:Rigに内臓のオート・アンテナチューナに頼るか、外付けの直下型チューナを使います。 ただしRig内蔵のチューナはリアクティブな負荷に対する整合範囲が狭くてうまく行かないことがあるようです。

ここでは(2)の方法を採用しました。 Blogに計算式を書くと嫌がられるので省きますがアンテナ関係の書籍に計算方法が出ています。 追加になるインダクタンスは約0.4μHですからローディング・コイル(約20μH)に含めることは容易です。根元に入れるマッチング用コンデンサは計算では433pFですが近似値の470pFにします。耐圧500Vのディップド・マイカ・コンデンサを使いました。コンデンサは給電点に直接ハンダ付けします。(最終的には自己融着テープで覆って防水対策しました)

【トップ・エレメント】

ローディング・コイルから上部のエレメントはロッド・アンテナを使っています。6段の伸縮式で完全に伸ばすと101.5cm(ネジ部含む)あります。ずいぶん前のHAMフェアで調達したものです。拙宅の長期在庫品(不良在庫品とも言う)だった物を使いました。

先端には金属製の「コマ」が付いています。短縮アンテナの場合、良いコイルを使いしかも接地抵抗が低いと非常にHigh-Qなアンテナになります。

そのようなアンテナでは10W程度でも先端部が非常に高電位になり尖っているとコロナ放電することがあります。「コマ」が付いていれば大丈夫な場合も多いのですが更に容量冠も付けると放電対策には効果的です。(放電が始まるとSWRが悪くなります)

大型の容量冠はアンテナ短縮にも効果があって好都合です。円環を数本のスポークで保持する構造が一般的です。この製作例では構造を簡単にする目的で8の字型の容量冠を設けました。 手持ちのテフロン被覆銀メッキ線:φ1.0mmを使いました。被覆を剥いで要所をハンダ付けして固定しました。 できたらバネ性のある材料の方が好ましくて、燐青銅の細線にメッキしたものが手に入れば理想的です。

写真の部分がロッド・アンテナの1段分に相当します。この部分の伸縮で共振周波数は約470kHz上下できました。(10MHz付近で)

【10MHz Whip AntennaのSWR特性】

写真は10MHz ホイップ・アンテナのSWR特性です。(黄色のトレース)

10.0MHzを中心に上下500kHz幅で観測しています。 10.110MHzがSWRのボトムでSWR=1.3程度になりました。

インピーダンス・マッチング回路をもう少し追い込むと更にSWRを下げられるでしょう。しかしまずまずと言ったところでしょうか。

このアンテナは全長1.5mの超短縮型で・・・短縮率は80%でフルサイズの20%の長さしかありません。 原理上このようなアンテナが狭帯域な特性になるのはやむを得ません。

10MHz帯のバンド幅はたったの50kHzですが微調整なしではフルにカバーできません。 従ってオンジエアする際は先端を伸縮させ共振周波数を微調整します。 CWあるいはデジタルモードに合わせ先端をわずかに伸縮すれば常にベストな状態でオンジエアできます。 先端部に目印を付けておいたので素早くセットできます。

【アンテナは飛ばなくては・笑】

送信に使うアンテナは良く飛ばなくては価値がありません。聞こえるだけではダメです。

さっそく近所の空き地へ移動してテスト目的にオンジエアしてみました。

写真は自局電波の飛びがわかるPSKRと言うサイトの画面キャプチャです。これは10.136MHzのFT-8モードでCQを出した際の反応です。時刻は日没の30分ほど前で、トランシーバの送信パワーは50Wです。

こんな超短縮アンテナですが北米、オセアニアそして東欧方面にも届いているようです。 もちろんコンディションにも助けられていますがあまりにも輻射効率が悪いとちらほらしかレポートが上がってきません。 全長わずか1.5mのアンテナですがそこそこの飛びが期待できそうです。 これくらい飛んでくれればよく飛ぶアンテナとして満足できます。

今さらですが、このアンテナは「接地」が重要です。もし給電点の直近で良好なボディーアースができていないなら「磁石アース板」(←参照リンク)を併用します。 このオンジエアでも磁石アース板:800pFの物を2枚使いました。

【先に計算すべきでした】

センターローディング形式の短縮アンテナを計算するPCソフトを使っています。 アンテナ関係の書籍など参考にして目的とするアンテナの計算に特化したものです。 電卓での計算を補助する程度のもので元はプログラム電卓用でした。

計算の主目的はローディング・コイルのインダクタンス値を求めることにあります。 簡易なソフトですが計算で得られたインダクタンス値は実際とよく合うのでアンテナ作りに重宝しています。 25年ほどまえモバイルからHF帯にオンジエアしようと思ったときアンテナ製作にかなり苦労しました。問題はローディング・コイルに皆目見当がつかないことでした。それでインダクタンス値を算出するソフトを作りました。 今回の製作でも先に計算しておけば試行回数をいくらか減らせたはずでした。

ほかにコイル計算のソフトも使います。形状寸法・巻数からインダクタンスを計算するものと、逆に必要なインダクタンスに対する最適寸法と巻数を決めるものです。短縮アンテナにはコイルが付きものなのでこうしたソフトが役立ちます。 コイルの関係はネット上にも計算してくれるサイトがあって利用すると便利です。

車載用に限らず短縮アンテナの製作は手探りになりがちですが可能な計算は行なってなるべく根拠に基づいて作りたいと思っています。もちろん最後の詰めはカット&トライになりますけど。hi hi

【30m Bandホイップ・アンテナのまとめ】

各部をバラバラに説明したので分かり難かったと思います。まとめのために手書きのイラストを載せます。どんな形状のアンテナを作ったのかわかり易く伝われば幸いです。なお、上部が94cmとなっているのはやや縮めて使うことを想定しています。

モバイル用のアンテナを手作りするHAMがいなくなったためかHAM雑誌では製作記事を見かけなくなったようです。

適当な材料さえあれば手作りでメーカー製より輻射効率の良い・・・良く飛ぶアンテナが作れます。 自分の手を動かして飛びを楽しむHAMがもうちょっと増えてほしいものです。

このアンテナの寸法・形状はおもに手持ちの部材に合わせて決まったものです。拙宅の物置を探してたまたま見つけた材料で作りました。手持ちのジャンクも活用しました。 従って寸分違わずまったく同じように製作されることをお勧めするものではありません。

寸法を示すことでおおよそどんなものを作れば30mバンドのアンテナとして機能するか明確にできたらこのBlogの目的は達成できたと思います。

ぜひご自身の部品事情に合わせたアレンジでVY-FBなアンテナを製作されて下さい。さらに工夫することで、より良く飛ぶアンテナが作れるでしょう。

アンテナの手作りには苦労や悩みも付きものですが、良く飛ぶアンテナが出来上がったときの満足感はなかなか大きいものです。 アンテナは無線通信の核心に迫る技術分野ですからなかなか面白い世界です。奥深い領域でもあります。 そして好き勝手な形式のアンテナを次々試して遊べるなんてアマ無線局だけの特権です。(左はアンテナ取り付けのイメージ図) 次回Blogでは40m Band / 7MHz用のホイップ・アンテナを作ります。 ではまた。de JA9TTT/1

(つづく)fm

abstract

The 30m band is a new HAM band in Japan; it has been authorised since 1 April 1982. Only HAMs with an advanced licence can on-air in the 30 m band. Therefore, few HAM stations on the air are available, so existing antennas are limited. High performance 30m band antennas for mobile use are unlikely. If not, it is best to build your own. I build high efficiency 30m band antennas. (2024.02.24 de JA9TTT/1 Takahiro Kato)

【30m Bandとは】

30mバンドは10.100MHz〜10.150MHzの50kHz幅を持ったHAMバンドです。WARCバンドの一つで日本では1982年4月1日から割り当てられた比較的新しいHAMバンドです。かつてはSSBもオンエアできたのですが現在は狭帯域の電波モードしか許可されていません。 具体的にはCW(無線電信)やF1D(FT-8やJT-65などのデジタルモード)が代表的です。

7MHz(40m Band)と14MHz(20m Band)の中間にあって海外へもよく飛ぶ周波数ですが2アマ以上の資格が必要なHAMバンドです。 そのためニッチなHAMバンドの扱いであり市販のアンテナは限られているようです。 他のバンドとの抱き合わせ製品はあっても10MHz用のホイップアンテナのようなバンド専用品はほとんど選択肢がありません。

ニーズがない以上、既製品が少ないのはやむを得ないとして欲しくなるようなメーカー製品がないなら自分で作るしかありません。 どんなアンテナが欲しいかと言えば輻射効率に優れるアンテナです。 モバイル局は50Wに制限されています。そんなモバイル局ではあっても、できるだけ良い(強力な)電波が飛ばせるようなアンテナが欲しいものです。 いくらスマートで体裁が良くても飛ばないものはアンテナにあらず、ダミーロードなんてねえ・・・。(考え方は各局それぞれです・笑)

☆

よく飛ぶアンテナは誰しも欲しいでしょう。しかし車載アンテナは走行中の安全を考えて機械的な強度や構造を考えねばなりません。従って自ずから寸法・形状や構造に制限が生じます。それにいくら良く飛ぶとは言っても見た目が大げさで手軽さがなければ商品性はありません。メーカー品は「売れてなんぼ」のものなのでお客さんの購買意欲を誘うような方向へ向かいます。

CWやデジタルモードを走行しながら運用することはありません。危険なので試みない方が賢明です。 半固定での運用に限定すれば輻射効率を追求する方向のアンテナが作れるかも知れません。 材料や手加工の限界で理想通りは難しいとしても可能な範囲で良いアンテナを目指したいと思います。 望むものが無ければ「自分で作る」ということです。

【なせ30m Band(10MHz)なのか?】

HF帯のメジャーバンドは7MHz帯や14MHz帯です。それに対して10MHz帯はマイナー・バンドなので空いています。従って弱い局でも拾ってもらいやすいです。これが「なぜ」の答えです。 実際に各局運用の様子を見ると昼間は国内が、また早朝や夕刻にはDX局もよく入ってきます。 国内、海外と満遍なく楽しむには向いたバンドと考えてモバイルからHF帯オンジエア最初のバンドに選びました。

【ローディング・コイルが命】

ジャンク箱の奥深くからエアー・ダックス・コイルを発掘しました。 然るべきボビンに銅線を巻いて「良いコイル」を自作しようと思っているのです。 そのためにはどんな仕様の(インダクタンスの)コイルが必要か知る必要があります。

まずは既製品のコイルで様子を見ることにしました。 そのためにエアー・ダックス・コイルを使って実測によって必要なインダクタンスを求めたいと思います。

☆

初めはそう思っていたのですが、エアー・ダックス・コイルを評価したところ思っていたよりもQが高く高性能だとわかりました。 最終的にはそのままローディング・コイルとして使うことにしました。 ただし機械的な強度に乏し構造なので実装方法に工夫を要します。

このコイルはNo.401016という型番です。 直径が40mmで、太さ(線径)が1.0mmの錫メッキ線を巻線のピッチが1.6mm(=線と線の隙間が0.6mmのスペース巻き)になるように巻けば同等品が作れます。

30m Bandの短縮型ホイップアンテナを全長が約150cmのセンター・ローディング形式で作る場合、ローディング・コイルのインダクタンスは20μH前後になります。もちろん輻射エレメントの寸法・構造によって幾分かは違ってきますが、大幅に違うことはなくてほぼ近似のインダクタンス値になるはずです。

エアー・ダックスがなければ同等のインダクタンスが得られるコイルを巻けば良い訳です。 短縮アンテナはコイルが命ですから可能な限りHigh-Qが得られるよう巻きます。 上手に巻くとこのエアー・ダックスよりずっと良いコイルが作れます。

【インダクタンスを求める】

後ほどの話で出てきますが必要なコイルのインダクタンスは計算することもできます。輻射エレメントの形状寸法などが決まればかなり精度よく求まります。

初めに計算すれば良かったのですが、いきなり実測でインダクタンスを求めてしまいました。そのような方法でも良いわけです。写真がその様子です。 実験ですのでコイルは裸の状態です。サポートも単にハンダで止めただけなので機械的な強度はまったくありません。

まずはじめにコイルより下部と上部の輻射エレメントを製作します。 上下ともに最終形状に仕上げるのがポイントです。 上下のアンテナ・エレメントができたら中間にエアー・ダックス・コイルを仮止めして調整開始です。できるだけ最終に近い状態になるようコイルを取り付けておくと仕上げの調整が容易になります。

共振が確認でき、巻き数が確定できたらコイルのサポート構造を考えることになります。 最初の写真のようにコイル全体をプラ製の容器に収める方法を採用しました。

コイルは容器のふた部分に接着剤を使って固定しました。 アンテナを付けたまま高速走行できるほどの強度は見込めませんが着脱の繰り返しや少々の風圧くらいで壊れることはないでしょう。 走行しながら使うことは想定していませんが車載アンテナは「しなる」ことを考慮して接合部分に柔軟性を持たせる構造にします。

【タップを変え共振追求】

タップの位置を変えながら共振周波数が目的の10.125MHzあたりに来るように追い込みます。

コイルはタップが取り出しやすいように一回おきに凹ませておきます。 順次タップをクリップで掴みながら共振周波数を測定します。(nanoVNAを使いました)

これでコイル何回分が必要なのか実地でわかります。 No.401016の場合、29回巻きで良いようでした。(注:これは他の要素によって幾らか違ってきます) 今回、コイルはそのまま使ってしまうのでインダクタンス値は知らなくても問題ありません。しかし知っておけば後々役立つので実測しておきました。19.57μHありました。Qu=255でした。後ほど出てきますが、計算で求めたインダクタンス:20.23μHと実測値との誤差は-3%とわずかです。

オンジエアする前の微調整は上部エレメントの伸縮によって行ないます。 上部のエレメントは6段のロッド・アンテナ(テレスコーピック・アンテナ)を使っています。 コイルを調整して共振点を求める際は完全に伸ばさずに上部エレメント1段の半分相当分だけ縮めておきます。 あらかじめ伸縮両方向の「調整しろ」を確保しておきます。もちろん全部伸ばしておきバンドの低端に合わせると言った方法もアリです。

【インピーダンス・マッチング】

短縮型アンテナの給電点インピーダンスは50Ωにはなりません。効率の良い短縮アンテナなら必ず低くなるはずです。 このアンテナの場合、おおよそ17Ωくらいが見込まれます。

インピーダンス・マッチングにはいくつかの方法があります。

(1)マッチングトランスを使う方法:透磁率の大きなフェライトコアを使いオート・トランス形式のマッチングトランスを作ります。広帯域な特性が得られるため、オート・アンテナチューナがRigに内臓される以前はよく使われました。

(2)インピーダンスマッチング回路を設ける方法:アンテナチューナと同じ考えですが、コンデンサ:Cとインダクタ:Lを使ったタイプはインダクタをローディングコイルの一部に含める方法で簡略化できます。単に給電点にコンデンサを付けるだけで済みます。(写真の方法)

(3)何もつけない方法:Rigに内臓のオート・アンテナチューナに頼るか、外付けの直下型チューナを使います。 ただしRig内蔵のチューナはリアクティブな負荷に対する整合範囲が狭くてうまく行かないことがあるようです。

ここでは(2)の方法を採用しました。 Blogに計算式を書くと嫌がられるので省きますがアンテナ関係の書籍に計算方法が出ています。 追加になるインダクタンスは約0.4μHですからローディング・コイル(約20μH)に含めることは容易です。根元に入れるマッチング用コンデンサは計算では433pFですが近似値の470pFにします。耐圧500Vのディップド・マイカ・コンデンサを使いました。コンデンサは給電点に直接ハンダ付けします。(最終的には自己融着テープで覆って防水対策しました)

【トップ・エレメント】

ローディング・コイルから上部のエレメントはロッド・アンテナを使っています。6段の伸縮式で完全に伸ばすと101.5cm(ネジ部含む)あります。ずいぶん前のHAMフェアで調達したものです。拙宅の長期在庫品(不良在庫品とも言う)だった物を使いました。

先端には金属製の「コマ」が付いています。短縮アンテナの場合、良いコイルを使いしかも接地抵抗が低いと非常にHigh-Qなアンテナになります。

そのようなアンテナでは10W程度でも先端部が非常に高電位になり尖っているとコロナ放電することがあります。「コマ」が付いていれば大丈夫な場合も多いのですが更に容量冠も付けると放電対策には効果的です。(放電が始まるとSWRが悪くなります)

大型の容量冠はアンテナ短縮にも効果があって好都合です。円環を数本のスポークで保持する構造が一般的です。この製作例では構造を簡単にする目的で8の字型の容量冠を設けました。 手持ちのテフロン被覆銀メッキ線:φ1.0mmを使いました。被覆を剥いで要所をハンダ付けして固定しました。 できたらバネ性のある材料の方が好ましくて、燐青銅の細線にメッキしたものが手に入れば理想的です。

写真の部分がロッド・アンテナの1段分に相当します。この部分の伸縮で共振周波数は約470kHz上下できました。(10MHz付近で)

【10MHz Whip AntennaのSWR特性】

写真は10MHz ホイップ・アンテナのSWR特性です。(黄色のトレース)

10.0MHzを中心に上下500kHz幅で観測しています。 10.110MHzがSWRのボトムでSWR=1.3程度になりました。

インピーダンス・マッチング回路をもう少し追い込むと更にSWRを下げられるでしょう。しかしまずまずと言ったところでしょうか。

このアンテナは全長1.5mの超短縮型で・・・短縮率は80%でフルサイズの20%の長さしかありません。 原理上このようなアンテナが狭帯域な特性になるのはやむを得ません。

10MHz帯のバンド幅はたったの50kHzですが微調整なしではフルにカバーできません。 従ってオンジエアする際は先端を伸縮させ共振周波数を微調整します。 CWあるいはデジタルモードに合わせ先端をわずかに伸縮すれば常にベストな状態でオンジエアできます。 先端部に目印を付けておいたので素早くセットできます。

【アンテナは飛ばなくては・笑】

送信に使うアンテナは良く飛ばなくては価値がありません。聞こえるだけではダメです。

さっそく近所の空き地へ移動してテスト目的にオンジエアしてみました。

写真は自局電波の飛びがわかるPSKRと言うサイトの画面キャプチャです。これは10.136MHzのFT-8モードでCQを出した際の反応です。時刻は日没の30分ほど前で、トランシーバの送信パワーは50Wです。

こんな超短縮アンテナですが北米、オセアニアそして東欧方面にも届いているようです。 もちろんコンディションにも助けられていますがあまりにも輻射効率が悪いとちらほらしかレポートが上がってきません。 全長わずか1.5mのアンテナですがそこそこの飛びが期待できそうです。 これくらい飛んでくれればよく飛ぶアンテナとして満足できます。

今さらですが、このアンテナは「接地」が重要です。もし給電点の直近で良好なボディーアースができていないなら「磁石アース板」(←参照リンク)を併用します。 このオンジエアでも磁石アース板:800pFの物を2枚使いました。

【先に計算すべきでした】

センターローディング形式の短縮アンテナを計算するPCソフトを使っています。 アンテナ関係の書籍など参考にして目的とするアンテナの計算に特化したものです。 電卓での計算を補助する程度のもので元はプログラム電卓用でした。

計算の主目的はローディング・コイルのインダクタンス値を求めることにあります。 簡易なソフトですが計算で得られたインダクタンス値は実際とよく合うのでアンテナ作りに重宝しています。 25年ほどまえモバイルからHF帯にオンジエアしようと思ったときアンテナ製作にかなり苦労しました。問題はローディング・コイルに皆目見当がつかないことでした。それでインダクタンス値を算出するソフトを作りました。 今回の製作でも先に計算しておけば試行回数をいくらか減らせたはずでした。

ほかにコイル計算のソフトも使います。形状寸法・巻数からインダクタンスを計算するものと、逆に必要なインダクタンスに対する最適寸法と巻数を決めるものです。短縮アンテナにはコイルが付きものなのでこうしたソフトが役立ちます。 コイルの関係はネット上にも計算してくれるサイトがあって利用すると便利です。

車載用に限らず短縮アンテナの製作は手探りになりがちですが可能な計算は行なってなるべく根拠に基づいて作りたいと思っています。もちろん最後の詰めはカット&トライになりますけど。hi hi

【30m Bandホイップ・アンテナのまとめ】

各部をバラバラに説明したので分かり難かったと思います。まとめのために手書きのイラストを載せます。どんな形状のアンテナを作ったのかわかり易く伝われば幸いです。なお、上部が94cmとなっているのはやや縮めて使うことを想定しています。

モバイル用のアンテナを手作りするHAMがいなくなったためかHAM雑誌では製作記事を見かけなくなったようです。

適当な材料さえあれば手作りでメーカー製より輻射効率の良い・・・良く飛ぶアンテナが作れます。 自分の手を動かして飛びを楽しむHAMがもうちょっと増えてほしいものです。

このアンテナの寸法・形状はおもに手持ちの部材に合わせて決まったものです。拙宅の物置を探してたまたま見つけた材料で作りました。手持ちのジャンクも活用しました。 従って寸分違わずまったく同じように製作されることをお勧めするものではありません。

寸法を示すことでおおよそどんなものを作れば30mバンドのアンテナとして機能するか明確にできたらこのBlogの目的は達成できたと思います。

ぜひご自身の部品事情に合わせたアレンジでVY-FBなアンテナを製作されて下さい。さらに工夫することで、より良く飛ぶアンテナが作れるでしょう。

アンテナの手作りには苦労や悩みも付きものですが、良く飛ぶアンテナが出来上がったときの満足感はなかなか大きいものです。 アンテナは無線通信の核心に迫る技術分野ですからなかなか面白い世界です。奥深い領域でもあります。 そして好き勝手な形式のアンテナを次々試して遊べるなんてアマ無線局だけの特権です。(左はアンテナ取り付けのイメージ図) 次回Blogでは40m Band / 7MHz用のホイップ・アンテナを作ります。 ではまた。de JA9TTT/1

(つづく)fm

登録:

投稿 (Atom)